SiFive bekerjasama dengan Imperas, memenuhi syarat model

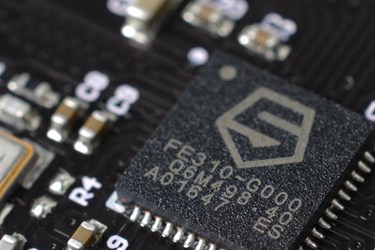

Perisian Imperas, pakar dalam platform maya dan simulasi perisian berprestasi tinggi, telah mengumumkan bahawa SiFive, peneraju industri dalam pemproses RISC-V dan penyelesaian silikon, telah memenuhi syarat modelnya untuk rangkaian Portal IP Core pemproses SiFive sepenuhnya.

Model simulasi adalah titik permulaan penting untuk penerokaan seni bina SoC awal, kerana pereka sistem menggunakan platform maya untuk menguji beban kerja aplikasi penuh dan set data untuk mengoptimumkan konfigurasi multicore.

Ketika reka bentuk dan pembangunan perkakasan berlangsung berdasarkan garis besar fungsional ini, model simulasi adalah asas yang menyokong prototaip maya untuk pengembangan perisian awal sebelum peranti silikon tersedia. Model-model ini berfungsi dengan kebanyakan IDE perisian dan debuger standard industri, dan tersedia dari Imperas dan rakan pengedar Imperas EDA yang diluluskan.

Ketepatan, prestasi, dan kebolehgunaan sangat penting ketika datang ke model simulasi pemproses dan model Imperas untuk IP pemproses SiFive adalah pandangan pengaturcara Instruction Accurate (IA) yang menggambarkan fungsi penuh IP teras, termasuk pengguna, istimewa, sistem, dan mod debug, ditambah pilihan konfigurasi untuk sambungan vektor RISC-V dan arahan tersuai.

Model-model ini dapat memberikan prestasi simulasi 100 hingga 1,000 MIPS pada PC hos yang dikonfigurasi dengan sederhana; sebagai contoh, model platform maya SiFive Freedom U540 SoC dengan lima teras CPU SiFive memacu SMP Linux dalam masa kurang dari 10 saat.

Kebolehgunaan penuh model Imperas digabungkan dengan alat nyahpepijat dan analisis Imperas yang menyokong tugas reka bentuk berbilang teras, termasuk port OS dan abstraksi untuk pembangunan aplikasi. Selain itu, simulator Imperas dengan simulasi pembentuk kod proprietari teknologi boleh disepadukan dalam persekitaran EDA standard lain seperti SystemC, SystemVerilog dan alat simulasi/emulasi terkenal daripada Cadence, Siemens EDA dan Synopsys serta tawaran berasaskan awan daripada Metrics Technologies.

Penyahpepijatan dan analisis perisian sangat penting dan alat Imperas membolehkan pembangun untuk meninjau aktiviti di SoC multicore penuh, termasuk interaksi merentasi hierarki reka bentuk untuk teras ke teras dan teras ke teras, dengan akses dan kawalan unik menggunakan perisian pembangunan tanpa pengubahsuaian.

Semakin banyak, fungsi perisian adalah sebahagian dari sistem pensijilan akhir dalam aplikasi kebolehpercayaan tinggi seperti Automotif, Mil-Aero, Perubatan, IoT Perindustrian, dan sistem keselamatan yang penting.

"Kebebasan reka bentuk RISC-V dan peluasan vektor mengubah batas tradisional antara fasa perisian dan perkakasan pembangunan SoC," kata Chris Jones, pemasaran produk VP, SiFive. "Model Imperas dari teras SiFive membantu pemaju dengan penerokaan seni bina SoC di seluruh fleksibiliti penuh Portofolio IP SiFive Core, dan menyokong pengembangan perisian awal, yang merupakan faktor penting dalam mengesahkan penyelesaian AI baru."

"Projek SoC adalah mengenai perkongsian; jurutera perkakasan dan perisian bekerjasama, dengan ekosistem penyokong yang lengkap, ”kata Phil Dworsky, Pengarah, Perikatan Strategik, SiFive. "Dengan kolaborasi Imperas ini, pelanggan bersama kami akan memanfaatkan ketersediaan model berkelayakan SiFive yang sesuai dengan aliran alat EDA arus perdana."

"Portofolio SiFive Core IP merangkumi spektrum RISC-V ISA, dari pengendali tertanam, hingga multiprosesor yang menyokong SMP Linux, ditambah dengan pemecut berasaskan vektor terbaru," kata Simon Davidmann, CEO, Imperas Software. "Ini adalah titik awal untuk generasi berikutnya peranti khusus domain di hampir semua segmen dan aplikasi pasar. Imperas bersedia menyokong reka bentuk yang menampilkan susunan single-core hingga array banyak-teras dengan model yang memenuhi syarat SiFive kami. "