SiFive collabore avec Imperas, qualifie les modèles

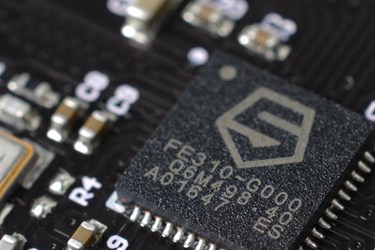

Imperas Software, spécialiste des plates-formes virtuelles et de la simulation logicielle haute performance, a annoncé que SiFive, le leader du secteur des processeurs RISC-V et des solutions silicium, a qualifié ses modèles pour la gamme complète du portefeuille Core IP de processeurs SiFive.

Les modèles de simulation sont un point de départ essentiel pour l'exploration architecturale précoce du SoC, car les concepteurs de systèmes utilisent des plates-formes virtuelles pour tester des charges de travail d'application complètes et des jeux de données afin d'optimiser les configurations multicœurs.

Au fur et à mesure que la conception et le développement du matériel progressent sur la base de ce schéma fonctionnel, le modèle de simulation est la base qui prend en charge les prototypes virtuels pour le développement logiciel précoce bien avant que les dispositifs en silicium soient disponibles. Ces modèles fonctionnent avec la plupart des IDE et débogueurs logiciels standard de l'industrie, et sont disponibles auprès d'Imperas et des partenaires de distribution Imperas EDA approuvés.

La précision, les performances et la convivialité sont essentielles lorsqu'il s'agit de modèles de simulation de processeur et les modèles Imperas pour l'IP de processeur SiFive sont une représentation de vue d'un programmeur Instruction Accurate (IA) de toutes les fonctionnalités de l'IP de base, y compris l'utilisateur, les privilèges, le système et modes de débogage, ainsi que les options de configuration pour les extensions vectorielles RISC-V et les instructions personnalisées.

Ces modèles sont capables de fournir des performances de simulation de 100 à 1,000 540 MIPS sur un PC hôte modestement configuré ; à titre d'exemple, le modèle de plate-forme virtuelle du SoC SiFive Freedom U10 avec cinq cœurs de processeur SiFive démarre SMP Linux en moins de XNUMX secondes.

La pleine convivialité des modèles Imperas est associée aux outils de débogage et d'analyse Imperas qui prennent en charge les tâches de conception multicœur, y compris le portage du système d'exploitation et les abstractions pour le développement d'applications. De plus, le simulateur Imperas avec simulation propriétaire de code-morphing sans souci peut être intégré à d'autres environnements EDA standard tels que SystemC, SystemVerilog et aux outils de simulation/émulation bien connus de Cadence, Siemens EDA et Synopsys, ainsi qu'à l'offre cloud de Metrics Technologies.

Le débogage et l'analyse du logiciel sont essentiels et les outils Imperas permettent aux développeurs d'introspecter les activités à travers le SoC multicœur complet, y compris les interactions à travers la hiérarchie de conception pour le cœur à cœur et le cœur à périphériques, avec un accès et un contrôle uniques à l'aide du logiciel sous développement sans modification.

De plus en plus, la fonctionnalité logicielle fait partie des certifications du système final dans les applications à haute fiabilité telles que l'automobile, le Mil-Aero, le médical, l'IoT industriel et d'autres systèmes critiques pour la sécurité.

« Les libertés de conception de RISC-V et des extensions vectorielles modifient les frontières traditionnelles entre les phases logicielles et matérielles du développement SoC », a déclaré Chris Jones, vice-président marketing produit, SiFive. « Les modèles Imperas des cœurs SiFive aident les développeurs à explorer l'architecture SoC dans toute la flexibilité du portefeuille IP SiFive Core, et prennent en charge le développement logiciel précoce, qui est un facteur essentiel dans la validation de nouvelles solutions d'IA. »

« Les projets SoC sont tous des partenariats ; ingénieurs matériels et logiciels travaillant ensemble, avec un écosystème complet de supporters », a déclaré Phil Dworsky, directeur des alliances stratégiques, SiFive. "Avec cette collaboration Imperas, nos clients communs bénéficieront de la disponibilité de modèles qualifiés SiFive compatibles avec les flux d'outils EDA traditionnels."

« Le portefeuille SiFive Core IP couvre le spectre de l'ISA RISC-V, des contrôleurs embarqués aux multiprocesseurs prenant en charge SMP Linux, en passant par les derniers accélérateurs vectoriels », a déclaré Simon Davidmann, PDG d'Imperas Software. « Ce sont les points de départ de la prochaine génération d'appareils spécifiques à un domaine dans presque tous les segments de marché et applications. Imperas est prêt à prendre en charge des conceptions comprenant des baies monocœur à plusieurs cœurs avec nos modèles qualifiés SiFive. »