SiFive ร่วมมือกับ Imperas เพื่อคัดเลือกโมเดล

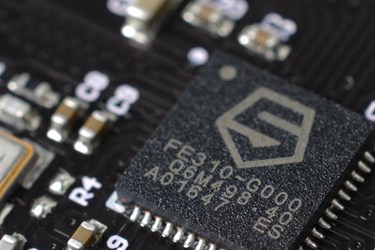

Imperas Software ผู้เชี่ยวชาญด้านแพลตฟอร์มเสมือนและการจำลองซอฟต์แวร์ประสิทธิภาพสูง ได้ประกาศว่า SiFive ผู้นำอุตสาหกรรมด้านโปรเซสเซอร์ RISC-V และโซลูชันซิลิคอน ได้ผ่านการรับรองโมเดลสำหรับผลิตภัณฑ์ Core IP Portfolio ของโปรเซสเซอร์ SiFive อย่างครบถ้วน

โมเดลจำลองเป็นจุดเริ่มต้นที่จำเป็นสำหรับการสำรวจสถาปัตยกรรม SoC ในช่วงต้น เนื่องจากผู้ออกแบบระบบใช้แพลตฟอร์มเสมือนเพื่อทดสอบเวิร์กโหลดของแอปพลิเคชันและชุดข้อมูลทั้งหมดเพื่อเพิ่มประสิทธิภาพการกำหนดค่าแบบมัลติคอร์

เนื่องจากการออกแบบและพัฒนาฮาร์ดแวร์ดำเนินไปตามโครงร่างการทำงานนี้ โมเดลจำลองจึงเป็นรากฐานที่สนับสนุนต้นแบบเสมือนสำหรับการพัฒนาซอฟต์แวร์ในยุคแรกๆ ก่อนที่อุปกรณ์ซิลิกอนจะพร้อมใช้งาน โมเดลเหล่านี้ใช้งานได้กับ IDE ซอฟต์แวร์มาตรฐานอุตสาหกรรมส่วนใหญ่และดีบักเกอร์ และมีจำหน่ายจาก Imperas และพันธมิตรการจัดจำหน่าย Imperas EDA ที่ได้รับอนุมัติ

ความแม่นยำ ประสิทธิภาพ และการใช้งานมีความสำคัญอย่างยิ่งเมื่อพูดถึงโมเดลจำลองโปรเซสเซอร์ และโมเดล Imperas สำหรับ IP โปรเซสเซอร์ SiFive คือการแสดงมุมมองของโปรแกรมเมอร์ Instruction Accurate (IA) ของฟังก์ชันการทำงานเต็มรูปแบบของ IP หลัก รวมถึงผู้ใช้ ผู้มีสิทธิพิเศษ ระบบ และ โหมดดีบัก รวมถึงตัวเลือกการกำหนดค่าสำหรับส่วนขยายเวกเตอร์ RISC-V และคำแนะนำที่กำหนดเอง

โมเดลเหล่านี้สามารถให้ประสิทธิภาพการจำลองได้ตั้งแต่ 100 ถึง 1,000 วินาทีของ MIPS บนพีซีโฮสต์ที่กำหนดค่าอย่างพอเหมาะ ตัวอย่างเช่น โมเดลแพลตฟอร์มเสมือนของ SiFive Freedom U540 SoC ที่มีคอร์ SiFive CPU ห้าคอร์จะบู๊ต SMP Linux ได้ภายใน 10 วินาที

การใช้งานโมเดล Imperas อย่างเต็มรูปแบบควบคู่ไปกับเครื่องมือดีบักและการวิเคราะห์ Imperas ที่รองรับงานออกแบบมัลติคอร์ รวมถึงการย้ายระบบปฏิบัติการและบทคัดย่อสำหรับการพัฒนาแอปพลิเคชัน นอกจากนี้ เครื่องจำลอง Imperas พร้อมการจำลองการดัดแปลงโค้ดที่เป็นกรรมสิทธิ์ เทคโนโลยี สามารถบูรณาการภายในสภาพแวดล้อม EDA มาตรฐานอื่นๆ เช่น SystemC, SystemVerilog และเครื่องมือการจำลอง/การจำลองที่รู้จักกันดีจาก Cadence, Siemens EDA และ Synopsys รวมถึงข้อเสนอบนคลาวด์จาก Metrics Technologies

การดีบักและการวิเคราะห์ซอฟต์แวร์มีความสำคัญอย่างยิ่ง และเครื่องมือ Imperas ช่วยให้นักพัฒนาสามารถทบทวนกิจกรรมใน SoC แบบมัลติคอร์แบบเต็มได้ รวมถึงการโต้ตอบข้ามลำดับชั้นการออกแบบสำหรับคอร์-ทู-คอร์และคอร์-ทู-อุปกรณ์ต่อพ่วง ด้วยการเข้าถึงและการควบคุมที่ไม่เหมือนใครโดยใช้ซอฟต์แวร์ภายใต้ การพัฒนาโดยไม่ต้องดัดแปลง

ฟังก์ชันซอฟต์แวร์เป็นส่วนหนึ่งของการรับรองระบบปลายทางในแอปพลิเคชันที่มีความน่าเชื่อถือสูงมากขึ้นเรื่อยๆ เช่น ยานยนต์, Mil-Aero, การแพทย์, IoT อุตสาหกรรม และระบบอื่นๆ ที่มีความสำคัญต่อความปลอดภัย

“เสรีภาพในการออกแบบของ RISC-V และส่วนขยายเวกเตอร์กำลังเปลี่ยนขอบเขตดั้งเดิมระหว่างขั้นตอนของซอฟต์แวร์และฮาร์ดแวร์ของการพัฒนา SoC” Chris Jones รองประธานฝ่ายการตลาดผลิตภัณฑ์ของ SiFive กล่าว "โมเดล Imperas ของแกน SiFive ช่วยให้นักพัฒนาสามารถสำรวจสถาปัตยกรรม SoC ได้อย่างยืดหยุ่นเต็มรูปแบบของ SiFive Core IP Portfolio และสนับสนุนการพัฒนาซอฟต์แวร์ในระยะเริ่มต้น ซึ่งเป็นปัจจัยสำคัญในการตรวจสอบความถูกต้องของโซลูชัน AI ใหม่"

“โครงการ SoC ล้วนเกี่ยวกับการเป็นหุ้นส่วน วิศวกรฮาร์ดแวร์และซอฟต์แวร์ทำงานร่วมกันโดยมีผู้สนับสนุนระบบนิเวศที่สมบูรณ์” Phil Dworsky ผู้อำนวยการ Strategic Alliances SiFive กล่าว “ด้วยการทำงานร่วมกันของ Imperas นี้ ลูกค้าร่วมกันของเราจะได้รับประโยชน์จากความพร้อมใช้งานของโมเดลที่ผ่านการรับรอง SiFive ที่เข้ากันได้กับโฟลว์เครื่องมือ EDA หลัก”

“กลุ่มผลิตภัณฑ์ SiFive Core IP ครอบคลุมสเปกตรัมของ RISC-V ISA ตั้งแต่ตัวควบคุมแบบฝัง ไปจนถึงโปรเซสเซอร์หลายตัวที่รองรับ SMP Linux รวมถึงตัวเร่งความเร็วแบบเวกเตอร์ล่าสุด” Simon Davidmann ซีอีโอของ Imperas Software กล่าว “สิ่งเหล่านี้เป็นจุดเริ่มต้นสำหรับอุปกรณ์เฉพาะโดเมนรุ่นต่อไปในเกือบทุกกลุ่มตลาดและแอพพลิเคชั่น Imperas พร้อมที่จะสนับสนุนการออกแบบที่มีอาร์เรย์แบบคอร์เดียวไปจนถึงหลายคอร์ด้วยโมเดลที่มีคุณสมบัติ SiFive ของเรา”