SiFive berkolaborasi dengan Imperas, model yang memenuhi syarat

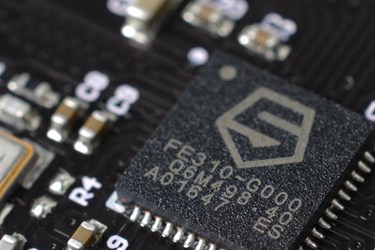

Imperas Software, spesialis platform virtual dan simulasi perangkat lunak berkinerja tinggi, telah mengumumkan bahwa SiFive, pemimpin industri dalam prosesor RISC-V dan solusi silikon, telah memenuhi syarat modelnya untuk rangkaian lengkap Portofolio Core IP prosesor SiFive.

Model simulasi adalah titik awal yang penting untuk eksplorasi arsitektur SoC awal, karena perancang sistem menggunakan platform virtual untuk menguji beban kerja aplikasi penuh dan kumpulan data untuk mengoptimalkan konfigurasi multicore.

Seiring kemajuan desain dan pengembangan perangkat keras berdasarkan garis besar fungsional ini, model simulasi adalah fondasi yang mendukung prototipe virtual untuk pengembangan perangkat lunak awal jauh sebelum perangkat silikon tersedia. Model ini bekerja dengan sebagian besar IDE dan debugger perangkat lunak standar industri, dan tersedia dari Imperas dan mitra distribusi EDA Imperas yang disetujui.

Akurasi, kinerja, dan kegunaan sangat penting dalam hal model simulasi prosesor dan model Imperas untuk IP prosesor SiFive adalah representasi tampilan programmer Instruction Accurate (IA) dari fungsionalitas penuh IP inti, termasuk pengguna, hak istimewa, sistem, dan mode debug, ditambah opsi konfigurasi untuk ekstensi vektor RISC-V dan instruksi khusus.

Model-model ini mampu memberikan kinerja simulasi 100-an hingga 1,000-an MIPS pada PC host yang dikonfigurasi secara sederhana; sebagai contoh, model platform virtual SoC SiFive Freedom U540 dengan lima inti CPU SiFive mem-boot SMP Linux dalam waktu kurang dari 10 detik.

Kegunaan penuh model Imperas digabungkan dengan alat debug dan analisis Imperas yang mendukung tugas desain multicore, termasuk porting OS dan abstraksi untuk pengembangan aplikasi. Selain itu, simulator Imperas dengan simulasi pengubahan kode berpemilik teknologi dapat diintegrasikan dalam lingkungan EDA standar lainnya seperti SystemC, SystemVerilog, dan alat simulasi/emulasi terkenal dari Cadence, Siemens EDA, dan Synopsys ditambah penawaran berbasis cloud dari Metrics Technologies.

Debug dan analisis perangkat lunak sangat penting dan alat Imperas memungkinkan pengembang untuk mengintrospeksi aktivitas di seluruh SoC multicore penuh, termasuk interaksi di seluruh hierarki desain untuk inti-ke-inti dan inti-ke-periferal, dengan akses dan kontrol unik menggunakan perangkat lunak di bawah pengembangan tanpa modifikasi.

Semakin, fungsionalitas perangkat lunak merupakan bagian dari sertifikasi sistem akhir dalam aplikasi dengan keandalan tinggi seperti Otomotif, Mil-Aero, Medis, IoT Industri, dan sistem kritis keselamatan lainnya.

“Kebebasan desain RISC-V dan ekstensi vektor mengubah batas tradisional antara fase perangkat lunak dan perangkat keras dari pengembangan SoC,” kata Chris Jones, VP pemasaran produk, SiFive. “Model Imperas dari inti SiFive membantu pengembang dengan eksplorasi arsitektur SoC di seluruh fleksibilitas penuh Portofolio IP Inti SiFive, dan mendukung pengembangan perangkat lunak awal, yang merupakan faktor penting dalam memvalidasi solusi AI baru.”

“Proyek SoC adalah tentang kemitraan; insinyur perangkat keras dan perangkat lunak bekerja sama, dengan ekosistem pendukung yang lengkap,” kata Phil Dworsky, Direktur, Aliansi Strategis, SiFive. “Dengan kolaborasi Imperas ini, pelanggan bersama kami akan mendapat manfaat dari ketersediaan model berkualitas SiFive yang kompatibel dengan aliran alat EDA arus utama.”

“Portofolio SiFive Core IP mencakup spektrum RISC-V ISA, dari pengontrol tertanam, hingga multiprosesor yang mendukung SMP Linux, ditambah akselerator berbasis vektor terbaru,” kata Simon Davidmann, CEO, Imperas Software. “Ini adalah titik awal untuk generasi berikutnya dari perangkat khusus domain di hampir semua segmen pasar dan aplikasi. Imperas siap mendukung desain yang menampilkan susunan inti tunggal hingga banyak inti dengan model berkualifikasi SiFive kami.”