SiFive arbeitet mit Imperas zusammen, qualifiziert Models

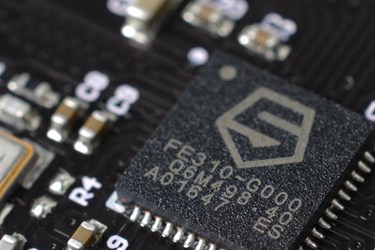

Imperas Software, ein Spezialist für virtuelle Plattformen und leistungsstarke Softwaresimulation, hat bekannt gegeben, dass SiFive, der Branchenführer bei RISC-V-Prozessoren und Siliziumlösungen, seine Modelle für die gesamte Palette des SiFive-Prozessor-Core-IP-Portfolios qualifiziert hat.

Simulationsmodelle sind ein wesentlicher Ausgangspunkt für die frühe Erforschung der SoC-Architektur, da Systemdesigner virtuelle Plattformen verwenden, um vollständige Anwendungsworkloads und Datensätze zu testen, um Multicore-Konfigurationen zu optimieren.

Während Hardwaredesign und -entwicklung basierend auf diesem funktionalen Entwurf fortschreiten, ist das Simulationsmodell die Grundlage, die virtuelle Prototypen für die frühe Softwareentwicklung unterstützt, lange bevor Siliziumbauteile verfügbar sind. Diese Modelle funktionieren mit den meisten branchenüblichen Software-IDEs und Debuggern und sind bei Imperas und zugelassenen Imperas EDA-Vertriebspartnern erhältlich.

Genauigkeit, Leistung und Benutzerfreundlichkeit sind entscheidend, wenn es um Prozessorsimulationsmodelle geht, und die Imperas-Modelle für SiFive-Prozessor-IP sind eine Anweisungsgenaue (IA)-Darstellung der vollständigen Funktionalität des Kern-IP, einschließlich Benutzer, privilegierte, System- und Debug-Modi sowie die Konfigurationsoptionen für die RISC-V-Vektorerweiterungen und benutzerdefinierte Anweisungen.

Diese Modelle sind in der Lage, eine Simulationsleistung von 100s bis 1,000s MIPS auf einem bescheiden konfigurierten Host-PC zu liefern; So bootet beispielsweise das virtuelle Plattformmodell des SiFive Freedom U540 SoC mit fünf SiFive CPU-Kernen SMP Linux in weniger als 10 Sekunden.

Die volle Nutzbarkeit der Imperas-Modelle ist mit den Imperas-Debug- und Analysetools gekoppelt, die Multicore-Designaufgaben unterstützen, einschließlich Betriebssystemportierung und Abstraktionen für die Anwendungsentwicklung. Darüber hinaus der Imperas-Simulator mit proprietärer Code-Morphing-Simulation Technologie kann in andere Standard-EDA-Umgebungen wie SystemC, SystemVerilog und bekannte Simulations-/Emulationstools von Cadence, Siemens EDA und Synopsys sowie das cloudbasierte Angebot von Metrics Technologies integriert werden.

Software-Debugging und -Analyse sind von entscheidender Bedeutung, und die Imperas-Tools ermöglichen es Entwicklern, die Aktivitäten im gesamten Multicore-SoC zu untersuchen, einschließlich der Interaktionen über die Designhierarchie für Core-to-Core und Core-to-Peripherie, mit einzigartigem Zugriff und Kontrolle über die Software unter Entwicklung ohne Modifikation.

Softwarefunktionalität ist zunehmend Teil der Endsystemzertifizierungen in hochzuverlässigen Anwendungen wie Automotive, Mil-Aero, Medical, Industrial IoT und anderen sicherheitskritischen Systemen.

„Die Designfreiheiten von RISC-V und Vektorerweiterungen verändern die traditionellen Grenzen zwischen den Software- und Hardwarephasen der SoC-Entwicklung“, sagte Chris Jones, VP Product Marketing, SiFive. „Die Imperas-Modelle der SiFive-Cores helfen Entwicklern bei der Erkundung der SoC-Architektur über die volle Flexibilität des SiFive-Core-IP-Portfolios und unterstützen die frühe Softwareentwicklung, die ein entscheidender Faktor bei der Validierung neuer KI-Lösungen ist.“

„Bei SoC-Projekten dreht sich alles um Partnerschaften; Hardware- und Softwareingenieure arbeiten mit einem kompletten Ökosystem von Unterstützern zusammen“, sagte Phil Dworsky, Director, Strategic Alliances, SiFive. „Durch diese Zusammenarbeit mit Imperas werden unsere gemeinsamen Kunden von der Verfügbarkeit von SiFive-qualifizierten Modellen profitieren, die mit den gängigen EDA-Toolflows kompatibel sind.“

„Das SiFive Core IP-Portfolio deckt das Spektrum der RISC-V ISA ab, von eingebetteten Controllern bis hin zu Multiprozessoren, die SMP Linux unterstützen, sowie die neuesten vektorbasierten Beschleuniger“, sagte Simon Davidmann, CEO, Imperas Software. „Dies sind die Ansatzpunkte für die nächste Generation domänenspezifischer Geräte über nahezu alle Marktsegmente und Anwendungen hinweg. Imperas ist bereit, mit unseren SiFive-qualifizierten Modellen Designs von Single-Core- bis hin zu Many-Core-Arrays zu unterstützen.“