SiFive collabora con Imperas, qualifica i modelli

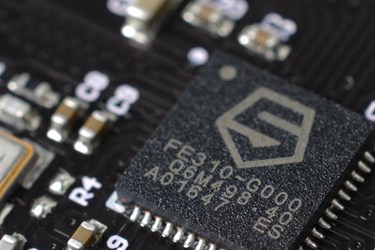

Imperas Software, specialista in piattaforme virtuali e simulazione software ad alte prestazioni, ha annunciato che SiFive, leader del settore nei processori RISC-V e nelle soluzioni in silicio, ha qualificato i suoi modelli per l'intera gamma del portafoglio Core IP di processori SiFive.

I modelli di simulazione sono un punto di partenza essenziale per l'esplorazione iniziale dell'architettura SoC, poiché i progettisti di sistemi utilizzano piattaforme virtuali per testare carichi di lavoro completi delle applicazioni e set di dati per ottimizzare le configurazioni multicore.

Man mano che la progettazione e lo sviluppo dell'hardware progrediscono in base a questo schema funzionale, il modello di simulazione è la base che supporta i prototipi virtuali per lo sviluppo iniziale del software ben prima che i dispositivi in silicio siano disponibili. Questi modelli funzionano con la maggior parte degli IDE e dei debugger software standard del settore e sono disponibili da Imperas e dai partner di distribuzione EDA approvati di Imperas.

L'accuratezza, le prestazioni e l'usabilità sono fondamentali quando si tratta di modelli di simulazione del processore e i modelli Imperas per l'IP del processore SiFive sono una rappresentazione della vista del programmatore Instruction Accurate (IA) della piena funzionalità dell'IP principale, inclusi utente, privilegiato, sistema e modalità di debug, oltre alle opzioni di configurazione per le estensioni vettoriali RISC-V e le istruzioni personalizzate.

Questi modelli sono in grado di fornire prestazioni di simulazione da 100 a 1,000 di MIPS su un PC host con configurazione modesta; ad esempio, il modello di piattaforma virtuale del SoC SiFive Freedom U540 con cinque core CPU SiFive avvia SMP Linux in meno di 10 secondi.

La piena usabilità dei modelli Imperas è abbinata agli strumenti di debug e analisi di Imperas che supportano attività di progettazione multicore, incluso il porting del sistema operativo e le astrazioni per lo sviluppo di applicazioni. Inoltre, il simulatore Imperas con simulazione proprietaria di morphing del codice la tecnologia può essere integrato in altri ambienti EDA standard come SystemC, SystemVerilog e noti strumenti di simulazione/emulazione di Cadence, Siemens EDA e Synopsys oltre all'offerta basata su cloud di Metrics Technologies.

Il debug e l'analisi del software sono fondamentali e gli strumenti Imperas consentono agli sviluppatori di analizzare le attività nell'intero SoC multicore, comprese le interazioni nella gerarchia di progettazione per le periferiche core-to-core e core-to-peripheral, con accesso e controllo univoci utilizzando il software sotto sviluppo senza modifiche.

Sempre più spesso, la funzionalità del software fa parte delle certificazioni del sistema finale in applicazioni ad alta affidabilità come Automotive, Mil-Aero, Medical, Industrial IoT e altri sistemi critici per la sicurezza.

"Le libertà di progettazione di RISC-V e le estensioni vettoriali stanno cambiando i confini tradizionali tra le fasi software e hardware dello sviluppo SoC", ha affermato Chris Jones, VP product marketing, SiFive. "I modelli Imperas dei core SiFive aiutano gli sviluppatori con l'esplorazione dell'architettura SoC attraverso la piena flessibilità del portafoglio IP SiFive Core e supportano lo sviluppo iniziale del software, che è un fattore critico nella convalida di nuove soluzioni AI".

“I progetti SoC riguardano tutti i partenariati; ingegneri hardware e software che lavorano insieme, con un ecosistema completo di sostenitori", ha affermato Phil Dworsky, Direttore, Strategic Alliances, SiFive. "Con questa collaborazione con Imperas, i nostri clienti comuni beneficeranno della disponibilità di modelli qualificati SiFive compatibili con i flussi di strumenti EDA tradizionali".

"Il portafoglio SiFive Core IP copre lo spettro del RISC-V ISA, dai controller embedded, ai multiprocessori che supportano SMP Linux, oltre ai più recenti acceleratori basati su vettori", ha affermato Simon Davidmann, CEO, Imperas Software. “Questi sono i punti di partenza per la prossima generazione di dispositivi specifici per dominio in quasi tutti i segmenti di mercato e le applicazioni. Imperas è pronta a supportare progetti con array da single-core a many-core con i nostri modelli qualificati SiFive”.