SiFive colabora con Imperas, califica modelos

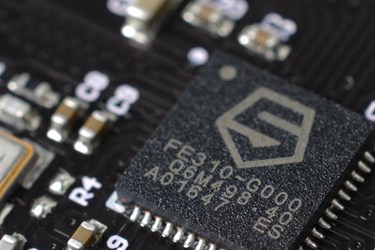

Imperas Software, especialista en plataformas virtuales y simulación de software de alto rendimiento, ha anunciado que SiFive, líder de la industria en procesadores RISC-V y soluciones de silicio, ha calificado sus modelos para la gama completa del Core IP Portfolio de procesadores SiFive.

Los modelos de simulación son un punto de partida esencial para la exploración arquitectónica de SoC temprana, ya que los diseñadores de sistemas utilizan plataformas virtuales para probar cargas de trabajo de aplicaciones completas y conjuntos de datos para optimizar configuraciones multinúcleo.

A medida que avanza el diseño y desarrollo de hardware en base a este esquema funcional, el modelo de simulación es la base que respalda los prototipos virtuales para el desarrollo temprano de software mucho antes de que los dispositivos de silicio estén disponibles. Estos modelos funcionan con la mayoría de los depuradores y IDE de software estándar de la industria, y están disponibles en Imperas y los socios de distribución de Imperas EDA aprobados.

La precisión, el rendimiento y la usabilidad son fundamentales cuando se trata de modelos de simulación de procesador y los modelos Imperas para IP de procesador SiFive son una representación de vista de programador de Instruction Accurate (IA) de la funcionalidad completa de la IP central, incluidos usuarios, privilegiados, sistema y modos de depuración, además de las opciones de configuración para las extensiones vectoriales RISC-V e instrucciones personalizadas.

Estos modelos pueden ofrecer un rendimiento de simulación de 100 a 1,000 de MIPS en una PC host modestamente configurada; como ejemplo, el modelo de plataforma virtual del SiFive Freedom U540 SoC con cinco núcleos de CPU SiFive arranca SMP Linux en menos de 10 segundos.

La total usabilidad de los modelos Imperas se combina con las herramientas de análisis y depuración de Imperas que admiten tareas de diseño multinúcleo, incluida la portabilidad del sistema operativo y las abstracciones para el desarrollo de aplicaciones. Además, el simulador Imperas con simulación patentada de transformación de código la tecnología se puede integrar en otros entornos EDA estándar, como SystemC, SystemVerilog y herramientas de simulación/emulación conocidas de Cadence, Siemens EDA y Synopsys, además de la oferta basada en la nube de Metrics Technologies.

La depuración y el análisis del software son fundamentales y las herramientas de Imperas permiten a los desarrolladores realizar una introspección de las actividades en todo el SoC multinúcleo completo, incluidas las interacciones en la jerarquía de diseño de núcleo a núcleo y de núcleo a periféricos, con acceso y control únicos utilizando el software en desarrollo sin modificaciones.

Cada vez más, la funcionalidad del software es parte de las certificaciones del sistema final en aplicaciones de alta confiabilidad, como Automotive, Mil-Aero, Medical, Industrial IoT y otros sistemas críticos para la seguridad.

“Las libertades de diseño de RISC-V y las extensiones vectoriales están cambiando los límites tradicionales entre las fases de software y hardware del desarrollo de SoC”, dijo Chris Jones, vicepresidente de marketing de productos de SiFive. "Los modelos Imperas de los núcleos SiFive ayudan a los desarrolladores con la exploración de la arquitectura de SoC en toda la flexibilidad de la cartera de IP de SiFive Core y respaldan el desarrollo temprano de software, que es un factor crítico en la validación de nuevas soluciones de inteligencia artificial".

“Los proyectos de SoC tienen que ver con asociaciones; ingenieros de hardware y software trabajando juntos, con un ecosistema completo de seguidores ”, dijo Phil Dworsky, Director de Alianzas Estratégicas de SiFive. "Con esta colaboración de Imperas, nuestros clientes mutuos se beneficiarán de la disponibilidad de modelos calificados SiFive que son compatibles con los flujos de herramientas EDA convencionales".

“La cartera de SiFive Core IP cubre el espectro de RISC-V ISA, desde controladores integrados hasta multiprocesadores compatibles con SMP Linux, además de los últimos aceleradores basados en vectores”, dijo Simon Davidmann, director ejecutivo de Imperas Software. “Estos son los puntos de partida para la próxima generación de dispositivos específicos de dominio en casi todos los segmentos y aplicaciones del mercado. Imperas está lista para admitir diseños con arreglos de un solo núcleo a varios núcleos con nuestros modelos calificados SiFive ”.