Aldec bringt HES-Board für ASIC- und SoC-Designs auf den Markt

Aldec hat das HES-VU19PD-ZU7EV auf den Markt gebracht, ein physisches ASIC/SoC-Prototyping- und Hardwareemulationsboard, das Designs mit einer Größe von etwa 83 Millionen ASIC-Gates aufnehmen kann.

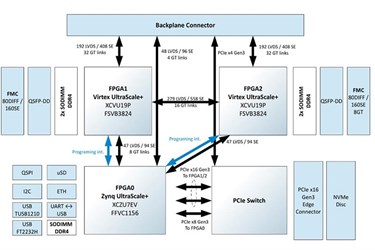

Der HES-VU19PD-ZU7EV verwendet nur zwei FPGAs für die Bereitstellung der Logik, was die FPGA Partitionierung und reduziert die Projektlaufzeit für Designs, die auf einen mittelgroßen ASIC oder SoC abzielen.

Für größere Designs können vier Boards über eine Hochgeschwindigkeits-Backplane verbunden werden (die Markteinführung ist für später im Jahr geplant), um das Äquivalent von etwa 332M ASIC-Gates bereitzustellen. Es wird auch möglich sein, Backplanes (bis zu drei) miteinander zu verbinden, um Designs von etwa 996M ASIC-Gates zu ermöglichen.

Die Logik des HES-VU19PD-7U7EV Modulen Bei den FPGAs handelt es sich jeweils um Virtex UltraScale+ VU19P-Geräte, Xilinxs bislang FPGA mit der höchsten Logikkapazität. Das Board verfügt außerdem über einen Xilinx Zynq UltraScale+ ZU7EV MPSoC, der als Host-Modul fungiert und über einen Quad-Core-ARM-Cortex-A53, Dual-Core-ARM-Cortex-R5-Echtzeitverarbeitungseinheiten und PCIe-Gen3-Embedded-IP verfügt.

Zibi Zalewski, General Manager der Hardware-Division von Aldec, kommentierte: „Für diese neue Plattform haben wir einen Großteil der Systemarchitektur unserer beliebten Dual-FPGA-Boards in unserer HES-7-Familie repliziert und die neuesten und größten UltraScale+ FPGAs von Xilinx bis Kapazität und Funktionalität für Emulations- und Prototyping-Szenarien erheblich erweitern. Außerdem bedeutet unsere Verwendung des Zynq US+-Geräts als Controller, dass es die Testbench für das Prototyping hosten kann. Tatsächlich sind die Prototyping- und Emulationsfunktionen unserer HES-Boards einzigartig bei Aldec.“

Zalewski wies auch darauf hin, dass eine Überarbeitung von HES-DVM, Aldecs vollautomatisierter und skalierbarer hybrider Verifikationsumgebung für SoC- und ASIC-Designs, in Vorbereitung ist. „Das wird die Leistungsfähigkeit des neuen Boards weiter freisetzen, zum Beispiel durch verbesserte Debug-Funktionen“, fügte er hinzu.

Der HES-VU19PD-7U7EV verfügt über ein PCIe-Switch-Gerät, das PCIe-x16-Gen-3-Verbindungen mit den Logikgeräten und PCIe-x8-Gen-3-Verbindungen mit dem Controller-FPGA bereitstellt.

Andere Schnittstellen umfassen QSFPDD auf jedem der Logik-FPGAs und Ethernet (1 Gb) und USB auf dem Steuerungs-FPGA.

In Bezug auf die Speicherschnittstelle bietet das Board fünf SODIMMs zur Aufnahme von externem DDR4-Speicher (zwei pro VU19P und einer für den ZU7EV) plus NVMe M.2 PCIe für zusätzlichen SSD-Speicher.

Das HES-VU19PD-7U7EV wird mit dem Softwarepaket HES Proto-AXI von Aldec geliefert, das alle notwendigen Treiber und Dienstprogramme für die Kommunikation mit und die Programmierung des Boards enthält. Für den schnellen Aufbau der Host-Verbindung stellt Aldec ein gebrauchsfertiges Image des Embedded Linux für das ZU7EV-Gerät bereit.