Aldec ra mắt bảng HES cho thiết kế ASIC & SoC

Aldec đã ra mắt HES-VU19PD-ZU7EV, một bảng mô phỏng phần cứng và tạo mẫu vật lý ASIC / SoC có thể đáp ứng các thiết kế có kích thước khoảng 83 triệu cổng ASIC.

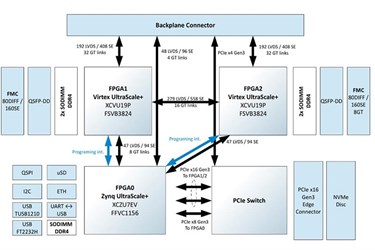

HES-VU19PD-ZU7EV chỉ sử dụng hai FPGA để cung cấp logic giúp đơn giản hóa FPGA phân vùng và giảm thời gian thực hiện dự án cho các thiết kế nhắm mục tiêu ASIC hoặc SoC cỡ trung bình.

Đối với các thiết kế lớn hơn, bốn bo mạch có thể được kết nối qua bảng nối đa năng tốc độ cao (dự kiến ra mắt vào cuối năm) để cung cấp khoảng 332M cổng ASIC tương đương. Nó cũng sẽ có thể kết nối các mặt sau với nhau (tối đa ba), để phục vụ cho các thiết kế của khoảng 996M cổng ASIC.

Logic của HES-VU19PD-7U7EV mô-đun FPGA đều là thiết bị Virtex UltraScale+ VU19P, FPGA có dung lượng logic cao nhất của Xilinx cho đến nay. Bo mạch này cũng có Xilinx Zynq UltraScale+ ZU7EV MPSoC hoạt động như mô-đun máy chủ và có ARM Cortex-A53 lõi tứ, bộ xử lý thời gian thực ARM Cortex-R5 lõi kép và IP nhúng PCIe Gen3.

Nhận xét Zibi Zalewski, Tổng Giám đốc Bộ phận Phần cứng của Aldec, cho biết: “Đối với nền tảng mới này, chúng tôi đã tái tạo phần lớn kiến trúc hệ thống của các bảng FPGA kép phổ biến trong gia đình HES-7 của chúng tôi và kết hợp UltraScale + FPGA mới nhất và lớn nhất từ Xilinx sang mở rộng đáng kể dung lượng và chức năng cho cả kịch bản mô phỏng và tạo mẫu. Ngoài ra, việc chúng tôi sử dụng thiết bị Zynq US + làm bộ điều khiển, có nghĩa là nó có thể lưu trữ testbench để tạo mẫu. Thật vậy, khả năng tạo mẫu và mô phỏng của bảng HES của chúng tôi là duy nhất của Aldec. ”

Zalewski cũng chỉ ra rằng một bản sửa đổi đối với HES-DVM, môi trường xác minh kết hợp hoàn toàn tự động và có thể mở rộng của Aldec cho các thiết kế SoC và ASIC, đang được triển khai. Ông nói thêm: “Điều đó sẽ tiếp tục giải phóng sức mạnh của bảng mới, thông qua khả năng gỡ lỗi nâng cao.

HES-VU19PD-7U7EV có thiết bị PCIe Switch cung cấp kết nối PCIe x16 Gen 3 với các thiết bị logic và kết nối PCIe x8 Gen 3 với bộ điều khiển FPGA.

Các giao diện khác bao gồm QSFPDD trên mỗi FPGA logic và Ethernet (1Gb) và USB trên FPGA điều khiển.

Về giao tiếp với bộ nhớ, bo mạch cung cấp năm SODIMM để cung cấp bộ nhớ DDR4 bên ngoài (hai cho mỗi VU19P và một cho ZU7EV) cộng với NVMe M.2 PCIe để lưu trữ thêm SSD.

HES-VU19PD-7U7EV được cung cấp với gói phần mềm HES Proto-AXI của Aldec bao gồm tất cả các trình điều khiển và tiện ích cần thiết để giao tiếp và lập trình bo mạch. Để nhanh chóng hiển thị kết nối máy chủ, Aldec cung cấp hình ảnh sẵn sàng sử dụng của Linux nhúng cho thiết bị ZU7EV.