Aldec lance la carte HES pour les conceptions ASIC et SoC

Aldec a lancé le HES-VU19PD-ZU7EV, une carte de prototypage physique et d'émulation matérielle ASIC/SoC pouvant accueillir des conceptions d'une taille d'environ 83 millions de portes ASIC.

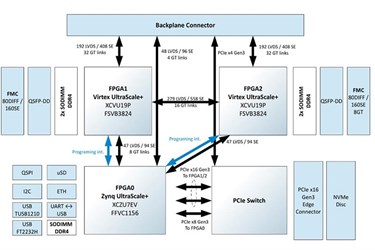

Le HES-VU19PD-ZU7EV n'utilise que deux FPGA pour fournir une logique qui simplifie FPGA le partitionnement et réduit le temps de lancement du projet pour les conceptions ciblant un ASIC ou un SoC de taille moyenne

Pour les conceptions plus grandes, quatre cartes peuvent être connectées via un fond de panier haute vitesse (dont le lancement est prévu plus tard dans l'année) pour fournir l'équivalent d'environ 332 millions de portes ASIC. Il sera également possible de connecter des fonds de panier ensemble (jusqu'à trois), pour prendre en charge des conceptions d'environ 996M de portes ASIC.

La logique du HES-VU19PD-7U7EV module Les FPGA sont tous deux des dispositifs Virtex UltraScale+ VU19P, le FPGA à capacité logique la plus élevée de Xilinx à ce jour. La carte comprend également un MPSoC Xilinx Zynq UltraScale+ ZU7EV qui fait office de module hôte et dispose d'un ARM Cortex-A53 quadricœur, d'unités de traitement en temps réel ARM Cortex-R5 double cœur et d'une IP intégrée PCIe Gen3.

Commentant Zibi Zalewski, directeur général de la division matériel d'Aldec, a déclaré : « Pour cette nouvelle plate-forme, nous avons reproduit une grande partie de l'architecture système de nos cartes FPGA doubles populaires dans notre famille HES-7 et incorporé les plus récents et les plus grands FPGA UltraScale+ de Xilinx à étendre considérablement la capacité et les fonctionnalités des scénarios d'émulation et de prototypage. De plus, notre utilisation de l'appareil Zynq US+ en tant que contrôleur, signifie qu'il peut héberger le banc d'essai pour le prototypage. En effet, les capacités de prototypage et d'émulation de nos cartes HES sont uniques à Aldec.

Zalewski a également indiqué qu'une révision de HES-DVM, l'environnement de vérification hybride entièrement automatisé et évolutif d'Aldec pour les conceptions SoC et ASIC, est en cours. « Cela libérera davantage la puissance de la nouvelle carte, grâce à des capacités de débogage améliorées, par exemple », a-t-il ajouté.

Le HES-VU19PD-7U7EV dispose d'un périphérique de commutation PCIe qui fournit des connexions PCIe x16 Gen 3 avec les périphériques logiques et des connexions PCIe x8 Gen 3 avec le contrôleur FPGA.

Les autres interfaces incluent QSFPDD sur chacun des FPGA logiques et Ethernet (1 Go) et USB sur le FPGA de contrôle.

En termes d'interfaçage avec la mémoire, la carte fournit cinq SODIMM pour accueillir la mémoire DDR4 externe (deux par VU19P et un pour le ZU7EV) plus NVMe M.2 PCIe pour un stockage SSD supplémentaire.

Le HES-VU19PD-7U7EV est fourni avec le progiciel HES Proto-AXI d'Aldec qui comprend tous les pilotes et utilitaires nécessaires pour communiquer avec et programmer la carte. Pour une mise en place rapide de la connexion hôte, Aldec fournit une image prête à l'emploi du Linux embarqué pour le périphérique ZU7EV.