Aldec melancarkan papan HES untuk reka bentuk ASIC & SoC

Aldec telah melancarkan HES-VU19PD-ZU7EV, sebuah prototaip fizikal ASIC / SoC dan papan emulasi perkakasan yang dapat memuatkan reka bentuk berukuran sekitar 83M ASIC gerbang.

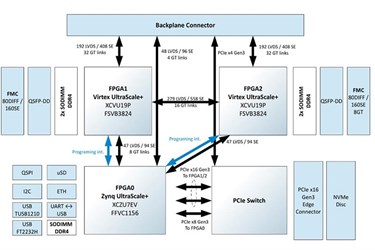

HES-VU19PD-ZU7EV menggunakan hanya dua FPGA untuk penyediaan logik yang mempermudah FPGA membuat partition dan mengurangkan masa pembesaran projek untuk reka bentuk yang mensasarkan ASIC atau SoC bersaiz sederhana.

Untuk reka bentuk yang lebih besar, empat papan boleh disambungkan melalui pesawat belakang berkelajuan tinggi (dijadualkan dilancarkan pada akhir tahun ini) untuk menyediakan setara dengan kira-kira 332M ASIC gerbang. Anda juga dapat menyambungkan pesawat belakang bersama (hingga tiga), untuk memenuhi reka bentuk kira-kira 996M ASIC gerbang.

Logik HES-VU19PD-7U7EV modul FPGA ialah kedua-dua peranti Virtex UltraScale+ VU19P, FPGA kapasiti logik tertinggi Xilinx setakat ini. Papan ini juga mempunyai Xilinx Zynq UltraScale+ ZU7EV MPSoC yang bertindak sebagai modul hos dan mempunyai empat teras ARM Cortex-A53, unit pemprosesan masa nyata ARM Cortex-R5 dwi-teras dan IP terbenam PCIe Gen3.

Mengulas Zibi Zalewski, Pengurus Besar Bahagian Perkakasan Aldec, berkata, "Untuk platform baru ini, kami telah mereplikasi sebahagian besar senibina sistem papan FPGA dwi yang popular dalam keluarga HES-7 kami dan menggabungkan UltraScale + FPGA terbaru dan terbesar dari Xilinx hingga memperluas keupayaan dan fungsi untuk kedua-dua senario peniruan dan prototaip. Selain itu, penggunaan peranti Zynq US + kami sebagai pengawal, ini bermaksud ia boleh menjadi hostbank untuk prototaip. Memang, kemampuan prototaip dan emulasi papan HES kami adalah unik untuk Aldec. "

Zalewski juga menunjukkan bahawa semakan kepada HES-DVM, persekitaran pengesahan hibrid Aldec sepenuhnya automatik dan berskala untuk reka bentuk SoC dan ASIC, sedang dalam proses. "Itu akan terus melancarkan kekuatan papan baru, melalui kemampuan debug yang dipertingkatkan, misalnya," tambahnya.

HES-VU19PD-7U7EV mempunyai peranti PCIe Switch yang menyediakan sambungan PCIe x16 Gen 3 dengan peranti logik dan sambungan PCIe x8 Gen 3 dengan pengawal FPGA.

Antara muka lain termasuk QSFPDD pada setiap FPGA logik dan Ethernet (1Gb) dan USB pada FPGA kawalan.

Dari segi penghubung dengan memori, papan menyediakan lima SODIMM untuk menampung memori DDR4 luaran (dua per VU19P dan satu untuk ZU7EV) ditambah NVMe M.2 PCIe untuk penyimpanan SSD tambahan.

HES-VU19PD-7U7EV dibekalkan dengan pakej perisian HES Proto-AXI Aldec yang merangkumi semua pemacu dan utiliti yang diperlukan untuk berkomunikasi dengan dan memprogram papan kenyataan. Untuk penyambungan host yang cepat, Aldec menyediakan gambar siap pakai Linux tertanam untuk peranti ZU7EV.