AldecがASICおよびSoC設計用のHESボードを発表

Aldecは、約19MASICゲートのサイズの設計に対応できるASIC / SoC物理プロトタイピングおよびハードウェアエミュレーションボードであるHES-VU7PD-ZU83EVを発売しました。

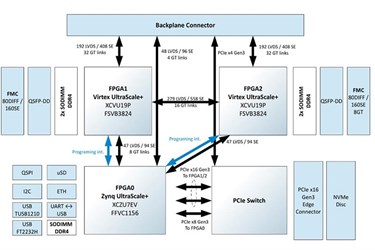

HES-VU19PD-ZU7EVは、ロジックの提供にXNUMXつのFPGAを使用するため、ロジックが簡素化されます。 FPGA 中規模のASICまたはSoCを対象とする設計では、パーティション分割を行い、プロジェクトの立ち上げ時間を短縮します。

より大きな設計の場合、332つのボードを高速バックプレーン(年内に発売予定)を介して接続して、約996MASICゲートに相当するものを提供できます。 また、バックプレーンを相互に接続して(最大XNUMXつ)、約XNUMXMASICゲートの設計に対応することもできます。

HES-VU19PD-7U7EVのロジック モジュール FPGA は両方とも Virtex UltraScale+ VU19P デバイスであり、ザイリンクス史上最高のロジック容量の FPGA です。 このボードには、ホスト モジュールとして機能し、クアッドコア ARM Cortex-A7、デュアルコア ARM Cortex-R53 リアルタイム プロセッシング ユニット、および PCIe Gen5 組み込み IP を備えた Xilinx Zynq UltraScale+ ZU3EV MPSoC も搭載されています。

Aldecのハードウェア部門のゼネラルマネージャーであるZibiZalewskiは、次のように述べています。「この新しいプラットフォームでは、HES-7ファミリの人気のあるデュアルFPGAボードのシステムアーキテクチャの多くを複製し、ザイリンクスからエミュレーションシナリオとプロトタイピングシナリオの両方の容量と機能を大幅に拡張します。 また、コントローラーとしてZynq US +デバイスを使用することは、プロトタイピング用のテストベンチをホストできることを意味します。 実際、HESボードのプロトタイピングおよびエミュレーション機能はAldec独自のものです。」

Zalewskiはまた、AldecのSoCおよびASIC設計向けの完全に自動化されたスケーラブルなハイブリッド検証環境であるHES-DVMの改訂が進行中であることを示しました。 「これにより、たとえば、強化されたデバッグ機能を通じて、新しいボードのパワーがさらに解き放たれます」と彼は付け加えました。

HES-VU19PD-7U7EVには、ロジックデバイスとのPCIe x16 Gen 3接続と、コントローラーFPGAとのPCIe x8 Gen3接続を提供するPCIeスイッチデバイスがあります。

その他のインターフェイスには、各ロジック FPGA の QSFPDD と、制御 FPGA のイーサネット (1Gb) および USB があります。

メモリとのインターフェースに関して、ボードは外部DDR4メモリを収容するための19つのSODIMM(VU7Pごとに2つ、ZUXNUMXEV用にXNUMXつ)と追加のSSDストレージ用のNVMe M.XNUMXPCIeを提供します。

HES-VU19PD-7U7EVには、AldecのHES Proto-AXIソフトウェアパッケージが付属しています。このパッケージには、ボードとの通信とプログラミングに必要なすべてのドライバーとユーティリティが含まれています。 ホスト接続をすばやく起動するために、AldecはZU7EVデバイス用の組み込みLinuxのすぐに使用できるイメージを提供します。