Aldec เปิดตัวบอร์ด HES สำหรับการออกแบบ ASIC & SoC

Aldec ได้เปิดตัว HES-VU19PD-ZU7EV ซึ่งเป็น ASIC/SoC physical prototyping และ hardware emulation board ที่สามารถรองรับการออกแบบขนาดประมาณ 83M ASIC gates

HES-VU19PD-ZU7EV ใช้ FPGA เพียงสองตัวสำหรับการจัดหาตรรกะซึ่งทำให้ง่ายขึ้น FPGA การแบ่งพาร์ติชั่นและลดเวลานำโปรเจ็กต์สำหรับการออกแบบที่กำหนดเป้าหมายเป็น ASIC หรือ SoC ขนาดกลาง

สำหรับการออกแบบที่ใหญ่ขึ้น บอร์ดสี่บอร์ดสามารถเชื่อมต่อผ่านแบ็คเพลนความเร็วสูง (กำหนดจะเปิดตัวในปลายปีนี้) เพื่อให้เทียบเท่ากับเกท ASIC ประมาณ 332 ล้านตัว นอกจากนี้ยังสามารถเชื่อมต่อแบ็คเพลนเข้าด้วยกัน (มากถึงสาม) เพื่อรองรับการออกแบบประตู ASIC ประมาณ 996M

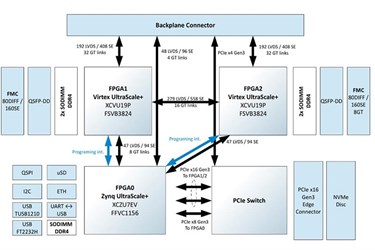

ตรรกะของ HES-VU19PD-7U7EV โมดูล FPGA เป็นทั้งอุปกรณ์ Virtex UltraScale+ VU19P ซึ่งเป็น FPGA ความจุลอจิกสูงสุดของ Xilinx จนถึงปัจจุบัน บอร์ดยังมีคุณสมบัติ Xilinx Zynq UltraScale+ ZU7EV MPSoC ซึ่งทำหน้าที่เป็นโมดูลโฮสต์ และมี ARM Cortex-A53 แบบ quad-core, หน่วยประมวลผลแบบเรียลไทม์ ARM Cortex-R5 แบบ dual-core และ IP แบบฝัง PCIe Gen3

Zibi Zalewski ผู้จัดการทั่วไปฝ่ายฮาร์ดแวร์ของ Aldec กล่าวว่า "สำหรับแพลตฟอร์มใหม่นี้ เราได้จำลองสถาปัตยกรรมระบบส่วนใหญ่ของบอร์ด FPGA แบบคู่ที่ได้รับความนิยมในตระกูล HES-7 ของเรา และรวม UltraScale+ FPGAs ใหม่ล่าสุดและใหญ่ที่สุดจาก Xilinx เข้ากับ ขยายขีดความสามารถและฟังก์ชันการทำงานอย่างมากสำหรับทั้งการจำลองสถานการณ์และการสร้างต้นแบบ นอกจากนี้ การใช้อุปกรณ์ Zynq US+ เป็นตัวควบคุม หมายความว่าอุปกรณ์นี้สามารถโฮสต์ testbench สำหรับการสร้างต้นแบบได้ อันที่จริง ความสามารถในการสร้างต้นแบบและการจำลองของบอร์ด HES ของเรานั้นมีเอกลักษณ์เฉพาะสำหรับ Aldec”

Zalewski ยังระบุด้วยว่าการแก้ไข HES-DVM ซึ่งเป็นสภาพแวดล้อมการตรวจสอบไฮบริดแบบอัตโนมัติและปรับขนาดได้ของ Aldec สำหรับการออกแบบ SoC และ ASIC อยู่ในขั้นตอนการดำเนินการ “นั่นจะช่วยปลดปล่อยพลังของบอร์ดใหม่ ผ่านความสามารถในการดีบั๊กที่เพิ่มขึ้น เป็นต้น” เขากล่าวเสริม

HES-VU19PD-7U7EV มีอุปกรณ์ PCIe Switch ซึ่งให้การเชื่อมต่อ PCIe x16 Gen 3 กับอุปกรณ์ลอจิกและการเชื่อมต่อ PCIe x8 Gen 3 กับคอนโทรลเลอร์ FPGA

อินเทอร์เฟซอื่นๆ ได้แก่ QSFPDD บนลอจิก FPGA และอีเทอร์เน็ต (1Gb) และ USB บนตัวควบคุม FPGA

ในแง่ของการเชื่อมต่อกับหน่วยความจำ บอร์ดมี SODIMM ห้าตัวสำหรับรองรับหน่วยความจำ DDR4 ภายนอก (สองตัวต่อ VU19P และอีกหนึ่งตัวสำหรับ ZU7EV) พร้อม NVMe M.2 PCIe สำหรับพื้นที่จัดเก็บ SSD เพิ่มเติม

HES-VU19PD-7U7EV มาพร้อมกับชุดซอฟต์แวร์ HES Proto-AXI ของ Aldec ซึ่งรวมถึงไดรเวอร์และยูทิลิตี้ที่จำเป็นทั้งหมดสำหรับการสื่อสารและเขียนโปรแกรมบอร์ด สำหรับการเชื่อมต่อโฮสต์อย่างรวดเร็ว Aldec ให้อิมเมจพร้อมใช้งานของ Linux แบบฝังสำหรับอุปกรณ์ ZU7EV