Aldec HES tabulam inducit pro consiliorum ASIC & SoC

Aldec HES-VU19PD-ZU7EV, ASIC/SoC physicas prototyping et ferramenta emulationis tabulas instruxit, quae consilia circiter 83M ASIC portarum magnitudine accommodare possunt.

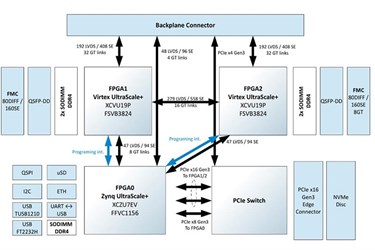

HES-VU19PD-ZU7EV duobus tantum FPGAs utitur ad praescriptum logicae quae simplificat. FPGA partiare et reducere project tempus adducunt tempus consiliorum molitionum mediarum amplitudo ASIC vel SoC.

Maioribus consiliis, quattuor tabulae per celeritatem backplani (accepti pro deducendae anno post in annum) coniungi possunt, ut instar portarum circiter 332M ASIC praebeat. Possibile etiam erit simul iungi puncta (usque ad tria), consilia ministrare circa portas 996M ASIC.

Logica HES-VU19PD-7U7EV Module FPGAs utriusque Virtex UltraScale+ VU19P sunt cogitationes, logicae Xilinx capacitas FPGA moderna. Tabula etiam notat Xilinx Zynq UltraScale+ ZU7EV MPSoC quae ad exercitum moduli agit et habet cortex ARM Cortex-A53, duplicatum ARM Cortex-R5 unitates reales temporis processus et Plu Gen3 infixa IP.

Commentans Zibi Zalewski, Procurator Generalis Divisionis Aldec's Hardware, dixit, "Ad hoc novum suggestum multum replicavimus de rationibus architecturae popularis nostrae tabulae dualis FPGA in nostra HES-7 familia, et novissimas et maximas UltraScale+ FPGAs ab Xilinx incorporavimus multum amplificatur capacitas et functionality ad tam aemulationem quam in missionibus prototypandis. Etiam, usus nostrae machinae Zynq US+ ut moderatoris, significat testbench offerre pro prototyping posse. Re quidem vera prototypatio et aemulatio facultatum tabularum nostrarum HES Aldec unica est».

Zalewski etiam indicavit recognitionem ad HES-DVM, Aldec plene automatum et scalabile verificationis hybridarum ambitum SoC et ASIC designandi, in pipelino esse. "Ille ulterius potestatem novae tabulae involvet, per facultates debug auctas, exempli gratia" addidit.

HES-VU19PD-7U7EV habet Plu Cie machinam quae praebet Plu x16 Gen 3 nexus cum logicae machinis et Plu x8 Gen 3 nexus cum moderatore FPGA.

Aliae interfaces includunt QSFPDD in singulis logicis FPGAs et Ethernet (1Gb) et USB in potestate FPGA.

Secundum memoriae intermediae, tabula quinque SODIMMs praebet ad memoriam externam DDR4 accommodatam (duo per VU19P et unum pro ZU7EV) plus NVMe M.2 Plu pro additis SSD repositionibus.

HES-VU19PD-7U7EV suppletur cum Aldec HES Proto-AXI involucrum programmatum in quo omnes rectores necessarii et utilitates comprehendunt communicandi cum tabula programmandi. Ad promptum nexum hospitii adducendum, Aldec imaginem Linux fixa in ZU7EV fabrica paratam praebet.