Aldec lanceert HES-bord voor ASIC- en SoC-ontwerpen

Aldec heeft de HES-VU19PD-ZU7EV gelanceerd, een ASIC/SoC fysieke prototyping en hardware-emulatiekaart die geschikt is voor ontwerpen van ongeveer 83M ASIC-poorten.

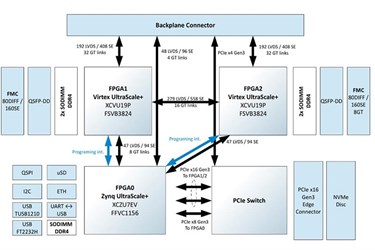

De HES-VU19PD-ZU7EV gebruikt slechts twee FPGA's voor het leveren van logica, wat FPGA partitionering en verkort de opstarttijd van projecten voor ontwerpen die zijn gericht op een middelgrote ASIC of SoC.

Voor grotere ontwerpen kunnen vier boards worden aangesloten via een high-speed backplane (gepland voor lancering later in het jaar) om het equivalent van ongeveer 332M ASIC-gates te leveren. Het zal ook mogelijk zijn om backplanes met elkaar te verbinden (maximaal drie), om te voorzien in ontwerpen van ongeveer 996M ASIC-poorten.

De logica van de HES-VU19PD-7U7EV module FPGA's zijn beide Virtex UltraScale+ VU19P-apparaten, Xilinx's FPGA met de hoogste logische capaciteit tot nu toe. Het bord beschikt ook over een Xilinx Zynq UltraScale+ ZU7EV MPSoC die fungeert als de hostmodule en heeft een quad-core ARM Cortex-A53, dual-core ARM Cortex-R5 real-time verwerkingseenheden en PCIe Gen3 ingebedde IP.

Zibi Zalewski, General Manager van Aldec's Hardware Division, zei: "Voor dit nieuwe platform hebben we veel van de systeemarchitectuur van onze populaire dubbele FPGA-kaarten in onze HES-7-familie gerepliceerd en de nieuwste en grootste UltraScale+ FPGA's van Xilinx opgenomen in vergroot de capaciteit en functionaliteit aanzienlijk voor zowel emulatie- als prototypingscenario's. Ons gebruik van het Zynq US+-apparaat als controller betekent ook dat het de testbank kan hosten voor prototyping. Inderdaad, de prototyping- en emulatiemogelijkheden van onze HES-boards zijn uniek voor Aldec.”

Zalewski gaf ook aan dat een herziening van HES-DVM, Aldec's volledig geautomatiseerde en schaalbare hybride verificatieomgeving voor SoC- en ASIC-ontwerpen, in de pijplijn zit. "Dat zal de kracht van het nieuwe bord verder ontketenen, bijvoorbeeld door verbeterde debug-mogelijkheden", voegde hij eraan toe.

De HES-VU19PD-7U7EV heeft een PCIe Switch-apparaat dat PCIe x16 Gen 3-verbindingen biedt met de logische apparaten en PCIe x8 Gen 3-verbindingen met de controller FPGA.

Andere interfaces zijn onder meer QSFPDD op elk van de logische FPGA's en Ethernet (1 Gb) en USB op de controle-FPGA.

Wat de interface met geheugen betreft, biedt het bord vijf SODIMM's voor het accommoderen van extern DDR4-geheugen (twee per VU19P en één voor de ZU7EV) plus NVMe M.2 PCIe voor extra SSD-opslag.

De HES-VU19PD-7U7EV wordt geleverd met Aldec's HES Proto-AXI-softwarepakket dat alle benodigde stuurprogramma's en hulpprogramma's bevat voor communicatie met en programmering van het bord. Om de hostverbinding snel tot stand te brengen, levert Aldec een kant-en-klaar beeld van de embedded Linux voor het ZU7EV-apparaat.