Aldec lanza la placa HES para diseños ASIC y SoC

Aldec ha lanzado el HES-VU19PD-ZU7EV, una placa de emulación de hardware y creación de prototipos físicos ASIC / SoC que puede acomodar diseños de aproximadamente 83M de puertas ASIC de tamaño.

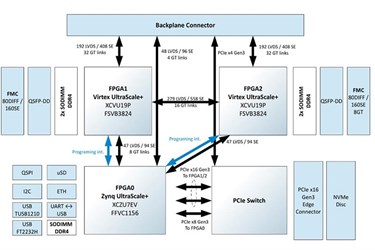

El HES-VU19PD-ZU7EV usa solo dos FPGA para la provisión de lógica que simplifica FPGA particionamiento y reduce el tiempo de ejecución del proyecto para los diseños que tienen como objetivo un ASIC o SoC de tamaño mediano.

Para diseños más grandes, se pueden conectar cuatro placas a través de una placa posterior de alta velocidad (programada para su lanzamiento más adelante en el año) para proporcionar el equivalente a aproximadamente 332M de puertas ASIC. También será posible conectar placas posteriores juntas (hasta tres), para adaptarse a diseños de puertas ASIC de aproximadamente 996M.

La lógica del HES-VU19PD-7U7EV módulo Los FPGA son dispositivos Virtex UltraScale+ VU19P, el FPGA de mayor capacidad lógica de Xilinx hasta la fecha. La placa también cuenta con un MPSoC Xilinx Zynq UltraScale+ ZU7EV que actúa como módulo host y tiene un ARM Cortex-A53 de cuatro núcleos, unidades de procesamiento en tiempo real ARM Cortex-R5 de doble núcleo e IP integrada PCIe Gen3.

Al comentar Zibi Zalewski, Gerente General de la División de Hardware de Aldec, dijo: “Para esta nueva plataforma, hemos replicado gran parte de la arquitectura del sistema de nuestras populares placas FPGA duales en nuestra familia HES-7 e incorporado las FPGA UltraScale + más nuevas y más grandes de Xilinx a amplía en gran medida la capacidad y la funcionalidad para escenarios de emulación y creación de prototipos. Además, nuestro uso del dispositivo Zynq US + como controlador significa que puede alojar el banco de pruebas para la creación de prototipos. De hecho, las capacidades de creación de prototipos y emulación de nuestras placas HES son exclusivas de Aldec ".

Zalewski también indicó que se está preparando una revisión de HES-DVM, el entorno de verificación híbrido escalable y totalmente automatizado de Aldec para diseños de SoC y ASIC. "Eso liberará aún más el poder de la nueva placa, a través de capacidades de depuración mejoradas, por ejemplo", agregó.

El HES-VU19PD-7U7EV tiene un dispositivo de conmutador PCIe que proporciona conexiones PCIe x16 Gen 3 con los dispositivos lógicos y conexiones PCIe x8 Gen 3 con el controlador FPGA.

Otras interfaces incluyen QSFPDD en cada uno de los FPGA lógicos y Ethernet (1 Gb) y USB en el FPGA de control.

En términos de interfaz con la memoria, la placa proporciona cinco SODIMM para acomodar la memoria DDR4 externa (dos por VU19P y uno para el ZU7EV) más NVMe M.2 PCIe para almacenamiento SSD adicional.

El HES-VU19PD-7U7EV se suministra con el paquete de software HES Proto-AXI de Aldec, que incluye todos los controladores y utilidades necesarios para comunicarse con la placa y programarla. Para una rápida activación de la conexión de host, Aldec proporciona una imagen lista para usar del Linux integrado para el dispositivo ZU7EV.