Aldec meluncurkan papan HES untuk desain ASIC & SoC

Aldec telah meluncurkan HES-VU19PD-ZU7EV, sebuah prototipe fisik ASIC/SoC dan papan emulasi perangkat keras yang dapat mengakomodasi desain dengan ukuran sekitar 83M gerbang ASIC.

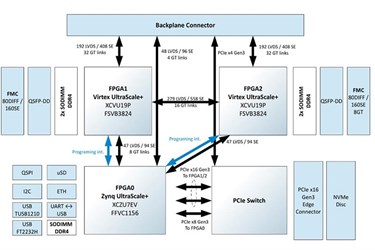

HES-VU19PD-ZU7EV hanya menggunakan dua FPGA untuk penyediaan logika yang menyederhanakan FPGA mempartisi dan mengurangi waktu pengerjaan proyek untuk desain yang menargetkan ASIC atau SoC berukuran sedang.

Untuk desain yang lebih besar, empat papan dapat dihubungkan melalui backplane berkecepatan tinggi (dijadwalkan untuk diluncurkan akhir tahun ini) untuk menyediakan setara dengan sekitar 332M gerbang ASIC. Dimungkinkan juga untuk menghubungkan backplane bersama-sama (hingga tiga), untuk memenuhi desain gerbang ASIC sekitar 996M.

Logika HES-VU19PD-7U7EV modul FPGA keduanya merupakan perangkat Virtex UltraScale+ VU19P, FPGA dengan kapasitas logika tertinggi di Xilinx hingga saat ini. Board ini juga dilengkapi dengan Xilinx Zynq UltraScale+ ZU7EV MPSoC yang bertindak sebagai modul host dan memiliki quad-core ARM Cortex-A53, unit pemrosesan real-time ARM Cortex-R5 dual-core, dan IP tertanam PCIe Gen3.

Mengomentari Zibi Zalewski, Manajer Umum Divisi Perangkat Keras Aldec, mengatakan, “Untuk platform baru ini, kami telah mereplikasi banyak arsitektur sistem papan FPGA ganda populer kami di keluarga HES-7 kami dan menggabungkan UltraScale+ FPGA terbaru dan terbesar dari Xilinx ke sangat memperluas kapasitas dan fungsionalitas untuk skenario emulasi dan prototipe. Selain itu, penggunaan perangkat Zynq US+ kami sebagai pengontrol, berarti perangkat ini dapat menghosting testbench untuk pembuatan prototipe. Memang, kemampuan prototipe dan emulasi papan HES kami unik untuk Aldec.”

Zalewski juga mengindikasikan bahwa revisi terhadap HES-DVM, lingkungan verifikasi hibrid Aldec yang sepenuhnya otomatis dan dapat diskalakan untuk desain SoC dan ASIC, sedang dalam proses. “Itu akan semakin melepaskan kekuatan papan baru, melalui peningkatan kemampuan debug, misalnya,” tambahnya.

HES-VU19PD-7U7EV memiliki perangkat PCIe Switch yang menyediakan koneksi PCIe x16 Gen 3 dengan perangkat logika dan koneksi PCIe x8 Gen 3 dengan pengontrol FPGA.

Antarmuka lainnya termasuk QSFPDD pada masing-masing FPGA logika dan Ethernet (1Gb) dan USB pada FPGA kontrol.

Dalam hal antarmuka dengan memori, board menyediakan lima SODIMM untuk menampung memori DDR4 eksternal (dua per VU19P dan satu untuk ZU7EV) ditambah NVMe M.2 PCIe untuk penyimpanan SSD tambahan.

HES-VU19PD-7U7EV dilengkapi dengan paket perangkat lunak HES Proto-AXI Aldec yang mencakup semua driver dan utilitas yang diperlukan untuk berkomunikasi dengan dan memprogram board. Untuk mempercepat koneksi host, Aldec menyediakan gambar siap pakai dari Linux tertanam untuk perangkat ZU7EV.