Aldec, ASIC 및 SoC 설계용 HES 보드 출시

Aldec은 크기가 약 19M ASIC 게이트의 설계를 수용할 수 있는 ASIC/SoC 물리적 프로토타이핑 및 하드웨어 에뮬레이션 보드인 HES-VU7PD-ZU83EV를 출시했습니다.

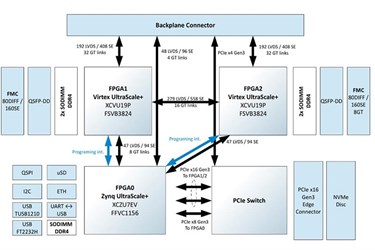

HES-VU19PD-ZU7EV는 로직 제공을 위해 단 XNUMX개의 FPGA를 사용하여 FPGA 중간 크기의 ASIC 또는 SoC를 대상으로 하는 설계의 경우 파티션을 나누고 프로젝트 시작 시간을 줄입니다.

더 큰 디자인의 경우 고속 백플레인(연말 출시 예정)을 통해 332개의 보드를 연결하여 약 996억 XNUMX만 ASIC 게이트에 해당하는 것을 제공할 수 있습니다. 또한 백플레인을 함께 연결(최대 XNUMX개)하여 약 XNUMXM ASIC 게이트 설계를 수용할 수 있습니다.

HES-VU19PD-7U7EV의 논리 모듈 FPGA는 둘 다 Virtex UltraScale+ VU19P 장치로 현재까지 Xilinx의 최고 로직 용량 FPGA입니다. 또한 이 보드에는 호스트 모듈 역할을 하는 Xilinx Zynq UltraScale+ ZU7EV MPSoC가 탑재되어 있으며 쿼드 코어 ARM Cortex-A53, 듀얼 코어 ARM Cortex-R5 실시간 처리 장치 및 PCIe Gen3 내장 IP가 있습니다.

Aldec의 하드웨어 사업부 총괄 책임자인 Zibi Zalewski는 다음과 같이 말했습니다. 에뮬레이션 및 프로토타이핑 시나리오 모두에 대한 용량과 기능을 크게 확장합니다. 또한 Zynq US+ 장치를 컨트롤러로 사용한다는 것은 프로토타이핑을 위한 테스트벤치를 호스팅할 수 있음을 의미합니다. 실제로 우리 HES 보드의 프로토타이핑 및 에뮬레이션 기능은 Aldec의 고유한 기능입니다.”

Zalewski는 또한 SoC 및 ASIC 설계를 위한 Aldec의 완전히 자동화되고 확장 가능한 하이브리드 검증 환경인 HES-DVM에 대한 개정이 파이프라인에 있다고 밝혔습니다. "예를 들어 향상된 디버그 기능을 통해 새 보드의 성능을 더욱 향상시킬 것입니다."라고 그는 덧붙였습니다.

HES-VU19PD-7U7EV에는 로직 장치와 PCIe x16 Gen 3 연결을 제공하고 컨트롤러 FPGA와 PCIe x8 Gen 3 연결을 제공하는 PCIe 스위치 장치가 있습니다.

다른 인터페이스에는 각 로직 FPGA의 QSFPDD와 제어 FPGA의 이더넷(1Gb) 및 USB가 있습니다.

메모리와의 인터페이스 측면에서 보드는 외부 DDR4 메모리를 수용하기 위한 19개의 SODIMM(VU7P당 2개, ZUXNUMXEV용 XNUMX개)과 추가 SSD 스토리지를 위한 NVMe M.XNUMX PCIe를 제공합니다.

HES-VU19PD-7U7EV는 보드와 통신하고 프로그래밍하는 데 필요한 모든 드라이버와 유틸리티가 포함된 Aldec의 HES Proto-AXI 소프트웨어 패키지와 함께 제공됩니다. 호스트 연결의 빠른 시작을 위해 Aldec은 ZU7EV 장치용 임베디드 Linux의 즉시 사용 가능한 이미지를 제공합니다.