Ziel ist es, „den Aufwand zu reduzieren, der erforderlich ist, um mehrere analoge IPs in einen Asic zu integrieren, indem das IP direkt in einen digitalen Design-Flow eingefügt werden kann“, so das Unternehmen. „Entscheidend ist, dass sich Kunden nicht mehr mit der Mixed-Signal-Grenze zwischen analog und digital auseinandersetzen müssen – die Subsysteme sehen genauso aus wie ein normaler Block digitaler IP, mit den Standardschnittstellen, die Ingenieure erwarten würden, wodurch sie einfach zu verstehen und zu handhaben sind .“

Zunächst bietet das Unternehmen drei Subsysteme an, für: Energiemanagement ('AgilePMU'), Prozess-Spannung- Temperaturmessung (PVT) ('agilePVT') und Schlafmanagement ('agileSMU').

Die IP-Blöcke innerhalb eines Subsystems stammen aus dem bestehenden Portfolio von Agile und können innerhalb des Digital Wrappers an die Kundenanforderungen angepasst werden, und es verifiziert das Mixed-Signal-Subsystem vorab, sodass der Kunde dies nicht tun muss.

„Die verpackten Subsysteme sind prozess- und gießereiunabhängig, und jedes Design ist für das spezifische PDK [Prozessdesign-Kit] des Kunden optimiert“, sagte Agile.

Zu den Leistungen gehören SystemVerilog-Modelle zur Integration in die bestehenden digitalen Verifizierungsabläufe der Kunden.

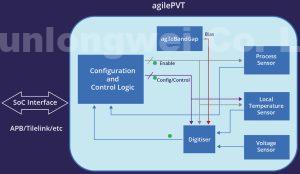

Der PVT Sensor (Top)-Subsystem verfügt über Prozess-, Spannungs- und Temperatursensoren, einen Referenzgenerator und eine digitale Steuerung zum An- und Abfahren. Statusmonitore liefern Echtzeit-Feedback.

Das Schlafmanagement-Subsystem (Recht) enthält typischerweise einen programmierbaren Oszillator für den Niederfrequenz-SoC-Betrieb und eine Reihe von Komparatoren, die verwendet werden können, um die Aufwachsequenz einzuleiten. Ein Power-On-Reset-Generator ist enthalten. Die Aktivitäten werden von einem digitalen Controller überwacht und Statusmonitore liefern Echtzeit-Feedback.

Agile Analog hat seinen Hauptsitz in Cambridge, Großbritannien.

Mehr sehen : IGBT-Module | LCD-Displays | Elektronische Komponenten