L'obiettivo è "ridurre lo sforzo richiesto per integrare più IP analogici in qualsiasi asic consentendo all'IP di essere inserito direttamente in un flusso di progettazione digitale", secondo la società. "Fondamentalmente, i clienti non devono più affrontare il confine del segnale misto tra analogico e digitale: i sottosistemi sembrano proprio un normale blocco di IP digitale, con le interfacce standard che gli ingegneri si aspetterebbero, rendendoli facili da capire e gestire .”

Inizialmente, l'azienda offre tre sottosistemi, per: gestione dell'alimentazione ("agilePMU"), processo-voltaggio-rilevamento della temperatura (PVT) ('agilePVT') e gestione del sonno ('agileSMU').

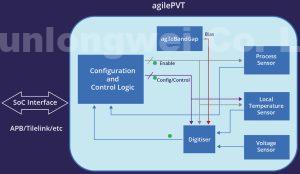

I blocchi IP all'interno di un sottosistema provengono dal portafoglio esistente di Agile e possono essere personalizzati in base alle esigenze del cliente all'interno del wrapper digitale e pre-verifica il sottosistema a segnale misto in modo che il cliente non debba farlo.

"I sottosistemi avvolti sono indipendenti dal processo e dalla fonderia e ogni progetto è ottimizzato per il PDK specifico del cliente [kit di progettazione del processo]", ha affermato Agile.

I risultati includono modelli SystemVerilog per l'integrazione nei flussi di verifica digitale esistenti dei clienti.

Il PVT sensore (top) ha sensori di processo, tensione e temperatura, un generatore di riferimento e un controller digitale per l'avvio e lo spegnimento. I monitor di stato forniscono feedback in tempo reale.

Il sottosistema di gestione del sonno (destra) conterrà tipicamente un oscillatore programmabile per il funzionamento del SoC a bassa frequenza e un numero di comparatori che possono essere utilizzati per avviare la sequenza di riattivazione. È incluso un generatore power-on-reset. Le attività sono supervisionate da un controller digitale e i monitor di stato forniscono feedback in tempo reale.

Agile Analog ha sede a Cambridge, nel Regno Unito.

Vedi di più: Moduli IGBT | display LCD | Componenti elettronici