同社によると、その目的は、「IP をデジタル設計フローに直接ドロップできるようにすることで、複数のアナログ IP を ASIC に統合するために必要な労力を削減すること」です。 「重要なのは、顧客がアナログとデジタルの間の混合信号の境界に対処する必要がなくなったことです。サブシステムは、エンジニアが期待する標準的なインターフェイスを備えたデジタル IP の通常のブロックのように見え、理解しやすく扱いやすいものになっています。 」

同社は当初、電源管理(「agilePMU」)、プロセス -電圧-温度 (PVT) センシング ('agilePVT')、および睡眠管理 ('agileSMU')。

サブシステム内の IP ブロックは、Agile の既存のポートフォリオからのもので、デジタル ラッパー内で顧客の要件に合わせてカスタマイズできます。また、混合信号サブシステムを事前検証するため、顧客はその必要がありません。

「ラップされたサブシステムはプロセスやファウンドリにとらわれず、各設計は顧客固有の PDK [プロセス設計キット] に合わせて最適化されています」と Agile 氏は述べています。

成果物には、顧客の既存のデジタル検証フローに統合するための SystemVerilog モデルが含まれています。

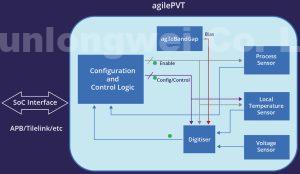

PVT センサー (top) サブシステムには、プロセス、電圧、および温度センサー、リファレンス ジェネレーター、および起動とシャットダウン用のデジタル コントローラーがあります。 ステータス モニターは、リアルタイムのフィードバックを提供します。

睡眠管理サブシステム (右) には通常、低周波数 SoC 動作用のプログラマブル オシレータと、ウェイクアップ シーケンスの開始に使用できる多数のコンパレータが含まれます。 パワーオンリセット発生器が含まれています。 アクティビティはデジタル コントローラーによって監視され、ステータス モニターはリアルタイムのフィードバックを提供します。

Agile Analog は、英国ケンブリッジに本社を置いています。