המטרה היא "להפחית את המאמץ הנדרש לשילוב כתובות IP אנלוגיות מרובות בכל ASIC על ידי מתן אפשרות להורדת ה-IP היישר לתוך זרימת עיצוב דיגיטלית", לדברי החברה. "באופן מכריע, לקוחות כבר לא צריכים להתמודד עם גבול האותות המעורבים בין אנלוגי לדיגיטלי - תת-המערכות נראות בדיוק כמו בלוק רגיל של IP דיגיטלי, עם הממשקים הסטנדרטיים שהמהנדסים מצפים להם, מה שהופך אותם לקלים להבנה ולטפל בהם ."

בתחילה, החברה מציעה שלוש תת-מערכות, עבור: ניהול צריכת חשמל ('agilePMU'), תהליך-מתחחישת טמפרטורה (PVT) ('agilePVT'), וניהול שינה ('agileSMU').

בלוקי ה-IP בתוך תת-מערכת הם מהפורטפוליו הקיים של Agile וניתן להתאים אותם לדרישות הלקוח בתוך העטיפה הדיגיטלית, והיא מאמתת מראש את תת-המערכת של אותות מעורבים כך שהלקוח לא יצטרך.

"תת המערכות העטופות הן אגנוסטיות לתהליכים וליציקה, וכל עיצוב מותאם ל-PDK הספציפי של הלקוח [ערכת עיצוב תהליכים]", אמר Agile.

התוצרים כוללים מודלים של SystemVerilog לשילוב בתזרימי האימות הדיגיטליים הקיימים של הלקוחות.

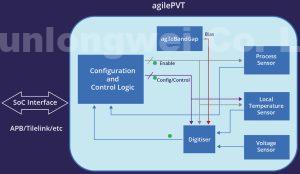

PVT חיישן (חלק עליון) תת-מערכת כוללת חיישני תהליך, מתח וטמפרטורה, מחולל ייחוס ובקר דיגיטלי להפעלה וכיבוי. צגי סטטוס מספקים משוב בזמן אמת.

תת-מערכת ניהול השינה (תקין) יכיל בדרך כלל מתנד הניתן לתכנות לפעולת SoC בתדר נמוך ומספר השוואות שניתן להשתמש בהן כדי להתחיל את רצף ההתעוררות. גנרטור לאיפוס הפעלה כלול. הפעילויות מפוקחות על ידי בקר דיגיטלי, וצגי מצב מספקים משוב בזמן אמת.

מטה Agile Analog נמצא בקיימברידג', בריטניה.

ראה עוד : מודולי IGBT | LCD מציג | רכיבים אלקטרוניים