El objetivo es “reducir el esfuerzo requerido para integrar múltiples IP analógicas en cualquier ASIC al permitir que la IP se suelte directamente en un flujo de diseño digital”, según la compañía. “De manera crucial, los clientes ya no necesitan lidiar con el límite de señal mixta entre analógico y digital: los subsistemas se ven como un bloque normal de IP digital, con las interfaces estándar que los ingenieros esperarían, haciéndolos fáciles de entender y manejar. .”

Inicialmente, la empresa ofrece tres subsistemas para: administración de energía ("agilePMU"), proceso-voltaje-sensor de temperatura (PVT) ('agilePVT') y gestión del sueño ('agileSMU').

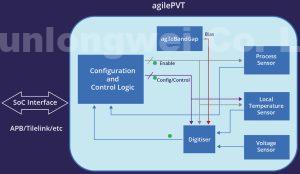

Los bloques de IP dentro de un subsistema son de la cartera existente de Agile y se pueden personalizar según los requisitos del cliente dentro de la envoltura digital, y verifica previamente el subsistema de señal mixta para que el cliente no tenga que hacerlo.

“Los subsistemas envueltos son independientes del proceso y de la fundición, y cada diseño está optimizado para el PDK [kit de diseño de procesos] específico del cliente”, dijo Agile.

Los entregables incluyen modelos SystemVerilog para la integración en los flujos de verificación digital existentes de los clientes.

El PVT sensor (parte superior) el subsistema tiene sensores de proceso, voltaje y temperatura, un generador de referencia y un controlador digital para el arranque y apagado. Los monitores de estado proporcionan información en tiempo real.

El subsistema de gestión del sueño (Derecho) normalmente contendrá un oscilador programable para el funcionamiento de SoC de baja frecuencia y una serie de comparadores que se pueden utilizar para iniciar la secuencia de activación. Se incluye un generador de encendido y reinicio. Las actividades son supervisadas por un controlador digital y los monitores de estado brindan retroalimentación en tiempo real.

Agile Analog tiene su sede en Cambridge, Reino Unido.

Ver más : Módulos IGBT | Pantallas LCD | Componentes y sistemas electrónicos