O objetivo é “reduzir o esforço necessário para integrar vários IPs analógicos em qualquer ASIC, permitindo que o IP seja descartado diretamente em um fluxo de design digital”, de acordo com a empresa. “Crucialmente, os clientes não precisam mais lidar com o limite de sinal misto entre analógico e digital – os subsistemas se parecem com um bloco normal de IP digital, com as interfaces padrão que os engenheiros esperariam, tornando-os fáceis de entender e manusear. .”

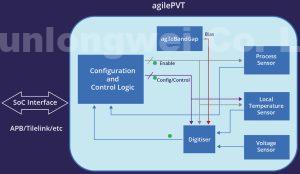

Inicialmente, a empresa está oferecendo três subsistemas, para: gerenciamento de energia ('agilePMU'), processamentoVoltagem- detecção de temperatura (PVT) ('agilePVT') e gerenciamento do sono ('agileSMU').

Os blocos de IP dentro de um subsistema são do portfólio existente da Agile e podem ser personalizados de acordo com os requisitos do cliente dentro do wrapper digital, e ele pré-verifica o subsistema de sinal misto para que o cliente não precise.

“Os subsistemas embalados são agnósticos de processo e fundição, e cada projeto é otimizado para o PDK [kit de projeto de processo] específico do cliente”, disse Agile.

Entregáveis incluem modelos SystemVerilog para integração em fluxos de verificação digital existentes dos clientes.

O PVT sensor (topo) possui sensores de processo, tensão e temperatura, gerador de referência e controlador digital para partida e desligamento. Monitores de status fornecem feedback em tempo real.

O subsistema de gerenciamento do sono (certo) geralmente contém um oscilador programável para operação SoC de baixa frequência e vários comparadores que podem ser usados para iniciar a sequência de despertar. Um gerador power-on-reset está incluído. As atividades são supervisionadas por um controlador digital e os monitores de status fornecem feedback em tempo real.

A Agile Analog está sediada em Cambridge, Reino Unido.

Veja mais : Módulos IGBT | Ecrãs LCD | Componentes Eletrônicos