เป้าหมายคือเพื่อ “ลดความพยายามที่จำเป็นในการรวม IP อะนาล็อกหลายตัวเข้ากับ asic ใด ๆ โดยปล่อยให้ IP ถูกทิ้งลงในโฟลว์การออกแบบดิจิทัลโดยตรง” ตามที่ บริษัท กล่าว “ที่สำคัญคือ ลูกค้าไม่จำเป็นต้องจัดการกับขอบเขตสัญญาณผสมระหว่างอะนาล็อกและดิจิทัลอีกต่อไป ระบบย่อยจะดูเหมือนบล็อก IP ดิจิทัลทั่วไป โดยมีอินเทอร์เฟซมาตรฐานที่วิศวกรคาดหวัง ทำให้เข้าใจและจัดการได้ง่าย ”

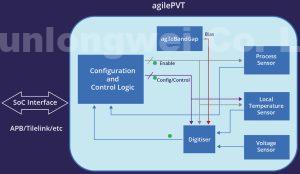

ในขั้นต้น บริษัทนำเสนอระบบย่อยสามระบบสำหรับ: การจัดการพลังงาน ('agilePMU'), กระบวนการ-แรงดันไฟฟ้า- การตรวจจับอุณหภูมิ (PVT) ('agilePVT') และการจัดการการนอนหลับ ('agileSMU')

บล็อก IP ภายในระบบย่อยมาจากพอร์ตโฟลิโอที่มีอยู่ของ Agile และสามารถปรับแต่งตามความต้องการของลูกค้าได้ภายในตัวห่อหุ้มดิจิทัล และจะตรวจสอบล่วงหน้าระบบย่อยสัญญาณผสมเพื่อให้ลูกค้าไม่ต้องดำเนินการเอง

“ระบบย่อยที่ห่อหุ้มเป็นกระบวนการและไม่เชื่อเรื่องพระเจ้าในการหล่อ และการออกแบบแต่ละอย่างได้รับการปรับให้เหมาะสมสำหรับ PDK [ชุดการออกแบบกระบวนการ] เฉพาะของลูกค้า” Agile กล่าว

สิ่งที่ส่งมอบได้รวมถึงโมเดล SystemVerilog สำหรับการรวมเข้ากับโฟลว์การตรวจสอบยืนยันทางดิจิทัลที่มีอยู่ของลูกค้า

PVT เซ็นเซอร์ (ด้านบน) ระบบย่อยมีเซ็นเซอร์กระบวนการ แรงดันและอุณหภูมิ เครื่องกำเนิดอ้างอิง และตัวควบคุมแบบดิจิทัลสำหรับการเริ่มต้นและปิดเครื่อง การตรวจสอบสถานะให้ข้อเสนอแนะตามเวลาจริง

ระบบย่อยการจัดการการนอนหลับ (ขวา) โดยทั่วไปจะมีออสซิลเลเตอร์ที่ตั้งโปรแกรมได้สำหรับการทำงานของ SoC ความถี่ต่ำ และตัวเปรียบเทียบจำนวนหนึ่งที่สามารถใช้เพื่อเริ่มต้นลำดับการปลุก รวมเครื่องกำเนิดไฟฟ้าแบบเปิดเครื่อง กิจกรรมต่างๆ จะถูกควบคุมโดยตัวควบคุมแบบดิจิทัล และตัวตรวจสอบสถานะจะให้ข้อเสนอแนะตามเวลาจริง

Agile Analog มีสำนักงานใหญ่อยู่ที่เมืองเคมบริดจ์ สหราชอาณาจักร

ดูเพิ่มเติม : โมดูล IGBT | จอแสดงผล LCD | ชิ้นส่วนอิเล็กทรอนิกส์