회사에 따르면 목표는 "IP를 디지털 설계 흐름에 바로 드롭할 수 있도록 하여 여러 아날로그 IP를 ASIC에 통합하는 데 필요한 노력을 줄이는 것"입니다. "결정적으로, 고객은 더 이상 아날로그와 디지털 사이의 혼합 신호 경계를 다룰 필요가 없습니다. 하위 시스템은 엔지니어가 기대하는 표준 인터페이스를 사용하여 디지털 IP의 일반 블록처럼 보이며 쉽게 이해하고 처리할 수 있습니다. .”

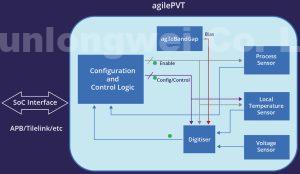

처음에 이 회사는 전원 관리('agilePMU'), 프로세스전압-온도(PVT) 감지('agilePVT') 및 수면 관리('agileSMU').

하위 시스템 내의 IP 블록은 Agile의 기존 포트폴리오에서 가져오고 디지털 래퍼 내부의 고객 요구 사항에 맞게 사용자 지정할 수 있으며 고객이 필요하지 않도록 혼합 신호 하위 시스템을 사전 검증합니다.

Agile은 "래핑된 하위 시스템은 프로세스 및 파운드리에 구애받지 않으며 각 설계는 고객의 특정 PDK[프로세스 설계 키트]에 최적화되어 있습니다."라고 말했습니다.

산출물에는 고객의 기존 디지털 검증 흐름에 통합하기 위한 SystemVerilog 모델이 포함됩니다.

PVT 감지기 (상단) 하위 시스템에는 시작 및 종료를 위한 프로세스, 전압 및 온도 센서, 참조 생성기 및 디지털 컨트롤러가 있습니다. 상태 모니터는 실시간 피드백을 제공합니다.

수면 관리 하위 시스템(연락해주세요)에는 일반적으로 저주파 SoC 작동을 위한 프로그래밍 가능 발진기와 웨이크업 시퀀스를 시작하는 데 사용할 수 있는 여러 비교기가 포함됩니다. power-on-reset 생성기가 포함되어 있습니다. 활동은 디지털 컨트롤러에 의해 감독되며 상태 모니터는 실시간 피드백을 제공합니다.

Agile Analog는 영국 케임브리지에 본사를 두고 있습니다.