Demokratisasi desain chip

Saat node proses 3nm mendekati kesiapan produksi, biaya pengembangan chip untuk itu telah naik lebih tinggi.

Namun ada dorongan yang berkembang untuk mendemokratisasikan desain chip: membawanya ke komunitas insinyur yang lebih luas, baik profesional maupun amatir. Ini mungkin tampak tugas yang mustahil tetapi gerakan ini bekerja pada teknologi yang jauh lebih tua karena secara bertahap menjadi lebih mudah diakses.

Ini sama sekali tidak sedramatis Hukum Moore untuk chip volume tinggi tetapi kurva pembelajaran silikon juga berfungsi untuk proses yang matang, terutama untuk biaya di muka seperti pembuatan topeng. Saat diperkenalkan, satu set topeng lengkap untuk proses 180nm dapat dengan mudah berharga $300,000 dan menghabiskan lebih dari setengah juta dolar untuk 130nm. Hari ini gambarannya sangat berbeda. Global Semikonduktor Survei industri asosiasi menemukan selama dua tahun terakhir, harga set topeng 180nm tidak lebih dari $60,000 dan seringkali di bawah $80,000 untuk set 130nm.

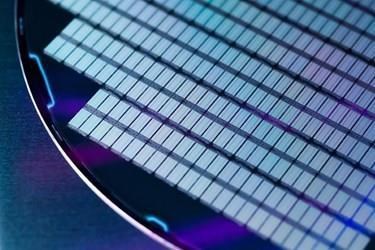

Bahkan sebelum masker proses matang turun harganya, satu cara berbiaya rendah ke dalam pembuatan prototipe ASIC dan bahkan pembuatan volume rendah terletak pada wafer multi-proyek (MPW) atau "shuttle", untuk menggunakan nama yang disukai oleh pengecoran TSMC. Ini memanfaatkan perbedaan antara ukuran sebagian besar sirkuit terpadu komersial (IC) dan area reticle yang digunakan alat litografi untuk mencetak fitur pada permukaan wafer. Anda bisa mendapatkan banyak desain yang berukuran 10 hingga milimeter persegi pada reticle yang mungkin berukuran 600 milimeter persegi. Di sisi lain, jumlah chip yang dapat Anda pilih untuk diterima mungkin terbatas hanya beberapa lusin tetapi cukup potensial untuk mendapatkan proyek ke titik di mana pendanaan eksternal merupakan pilihan.

Set topeng jauh dari satu-satunya biaya rekayasa dimuka. Alat dan IP sangat penting untuk desain apa pun, yang pada akhirnya dengan mudah mencapai jutaan. Salah satu pilihan untuk desainer miskin uang terletak pada alat berbiaya lebih rendah, seperti suite Tanner yang dijual oleh Siemens Digital Industries Software dan IP. Arm, misalnya, memasang kembali program DesignStart awal bulan ini, menawarkan akses ke pilihan inti yang berorientasi mikrokontroler tanpa menuntut biaya lisensi di muka, hanya royalti setelah produksi.

Kegiatan lain mencerminkan apa yang telah terjadi di banyak bagian pengembangan perangkat lunak dengan proyek seperti Eclipse: membangun lingkungan desain di sekitar alat sumber terbuka. Banyak tim desain chip yang sebagian sudah menggunakan open source, melalui bahasa pemodelan SystemC serta bahasa pemrograman Python, yang telah mendapatkan dukungan untuk mengontrol rangkaian uji yang digunakan dalam verifikasi RTL.

Inisiatif sumber terbuka

Inisiatif yang berpotensi penting adalah inisiatif OpenRoad dari badan penelitian AS, DARPA, dengan tujuan untuk membangun seperangkat alat desain sumber terbuka yang lebih komprehensif. Profesor Andrew Kahng dari University of California di San Diego dan peneliti utama proyek tersebut membayangkan lingkungan yang dapat menata dan menyesuaikan berbagai desain chip secara otomatis melalui kombinasi pembelajaran mesin dan apa yang dia sebut "partisi ekstrem", yang membagi chip ke dalam banyak modul kecil yang dioptimalkan secara independen.

Meskipun insinyur verifikasi telah menggunakan berbagai bentuk open source, hambatan untuk adopsinya semakin besar semakin dekat Anda dengan tape-out. Masalah terbesar terletak pada kit desain proses (PDK) yang disediakan oleh pengecoran yang sangat dilindungi oleh perjanjian kerahasiaan dan yang melarang berbagi apa pun.

Gambar di atas dan di bawah: Infrastruktur pengujian Caravel, yang dikembangkan oleh Antmicro, menyediakan ring I/O dan port uji yang dikelola oleh inti RISC-V bawaan

“Efabless tidak dapat merilis hasil yang sepenuhnya dapat digunakan kembali,” catat Ansell. “Seseorang seperti saya tidak bisa melihat bagaimana sesuatu diterapkan di gerbang. Ada sikap bermasalah dalam industri ini seputar berbagi.”

Ansell mengatakan Google tertarik pada kemampuan untuk berbagi pengetahuan atas dasar bahwa itu mempercepat kemajuan secara umum. “Dengan melambatnya hukum Moore, solusi inovatif baru akan dibutuhkan untuk memenuhi permintaan komputasi yang terus meningkat,” tambahnya.

Menyediakan komunitas yang lebih luas dengan akses ke desain silikon dapat memberikan jalan untuk menciptakan metode baru untuk perhitungan yang cenderung tidak terjadi melalui R&D tradisional. Untuk membantu mendorong hal itu, Ansell mulai mencoba meyakinkan para pengecoran untuk membuka PDK mereka. “Saya berbicara dengan banyak pengecoran. Dan saya ditertawakan oleh banyak pengecoran.”

Satu pengecoran datang ke ide: Skywater, sebuah perusahaan yang mengoperasikan fab di Minnesota yang dimiliki oleh Cypress Semiconductors hingga beberapa tahun yang lalu. “Kami dapat mencapai kesepakatan yang memungkinkan kami untuk merilis PDK 130nm di bawah lisensi sumber terbuka,” kata Ansell. Dapat diunduh dari Github, PDK menggunakan lisensi Apache 2.0 dan dapat dikloning oleh pengguna mana pun “tanpa harus meminta izin saya atau harus meminta izin Skywater. PDK sumber terbuka berarti kita dapat memiliki ASIC sumber terbuka sepenuhnya.”

Google dan eFabless kemudian mulai membangun layanan MPW yang memperluas kemungkinan desain ASIC kepada orang-orang tanpa puluhan ribu dolar untuk mendapatkan sesuatu kembali dari luar biasa. Agar memenuhi syarat untuk chip gratis, desainer harus siap untuk tidak hanya membuat desain mereka sendiri open source, mereka juga harus siap untuk memberikan sampel kepada pengguna yang tertarik untuk bekerja dengan desain dan silikon yang dihasilkan. “Desain Anda harus open source sampai ke GDS,” kata Ansell.

Pesawat ulang-alik akan mengembalikan sekitar seratus sampel, yang menurut Ansell sebagai jumlah yang cukup tinggi bagi pengguna untuk tidak khawatir menyediakan silikon berdasarkan permintaan kepada pengguna lain dan mencoba untuk memberikan kemungkinan berbagi perangkat keras sumber terbuka. “Open source memudahkan orang untuk berkolaborasi. Ini memungkinkan orang untuk mencoba hal-hal yang dulu mereka pikir terlalu berisiko. Itu membuatnya mudah dan murah untuk gagal, dan belajar dari kegagalan Anda.”

kendala

Kendala selanjutnya adalah persyaratan untuk menggunakan infrastruktur pengujian Caravel yang dikembangkan oleh Antmicro. Ini menyediakan ring I/O dan port uji yang dikelola oleh inti RISC-V bawaan. “Jika Anda sedang membangun chip uji untuk memulai, Anda memerlukan sesuatu seperti ini,” catat Efabless CTO dan salah satu pendiri Mohammed Kassem. Di tengah cincin I/O ini terdapat lubang 10 milimeter persegi untuk silikon khusus pengguna yang dapat digunakan untuk apa saja tanpa pembayaran.

Meskipun areanya relatif kecil, Ansell mengatakan desain digital yang kompleks dapat dicapai karena 130nm dapat menghasilkan lebih dari 1.5 juta gerbang. “Orang-orang sangat meremehkan kemampuan digital dari node yang lebih tua karena mereka sebagian besar digunakan akhir-akhir ini untuk menargetkan daya rendah dan desain analog,” catatnya.

Pengajuan untuk tahap pertama di Skywater pada proses 130nm ditutup pada November 2020 dan yang kedua ditutup untuk pengiriman pada pertengahan Juni, dengan suku cadang yang akan dikirimkan dari proses kedua itu ke pemilik proyek pada awal Desember. Google mendanai enam pesawat ulang-alik dalam waktu dekat. Efabless juga menawarkan MPW berbayar untuk merancang tim yang tidak ingin berkomitmen pada rute perangkat keras sumber terbuka sepenuhnya.

Pesawat ulang-alik pertama termasuk desain dari perusahaan seperti IBM dan Quicklogic.

“Tetapi hal yang paling menarik adalah bahwa 60 persen desainer belum pernah melakukan ASIC sebelumnya,” kata Ansell. “Keberhasilan program SkyWater menunjukkan bahwa ada permintaan besar untuk solusi terbuka dan kami sekarang memiliki beberapa minat awal dari pengecoran lain.”

Sementara bekerja pada node tingkat lanjut mendorong biaya desain yang lebih tinggi, meskipun dengan potensi imbalan yang sangat besar ketika chip yang dihasilkan masuk ke produksi, bekerja di ujung tombak pada desain demokratisasi mungkin terbukti sama pentingnya untuk mendorong kemajuan dalam industri.