Democratizzazione del design dei chip

Man mano che il nodo di processo a 3 nm si avvicina alla prontezza per la produzione, il costo di sviluppo dei chip per esso è aumentato di un'altra tacca.

Eppure c'è una spinta crescente verso la democratizzazione del design dei chip: portandolo a una comunità più ampia di ingegneri, sia professionisti che dilettanti. Questo può sembrare un compito impossibile, ma il movimento sta lavorando su tecnologie molto più vecchie man mano che diventano gradualmente più accessibili.

Non è nemmeno lontanamente drammatico come la legge di Moore per i chip ad alto volume, ma la curva di apprendimento del silicio funziona anche per i processi maturi, in particolare per i costi iniziali come la produzione di maschere. Al momento dell'introduzione, un set di maschere completo per il processo a 180 nm potrebbe facilmente costare $ 300,000 e raggiungere più di mezzo milione di dollari per 130 nm. Oggi il quadro è molto diverso. Il globale Semiconduttore Il sondaggio del settore dell'Associazione ha rilevato negli ultimi due anni che i prezzi dei set di maschere da 180 nm non erano superiori a $ 60,000 e spesso inferiori a $ 80,000 per i set da 130 nm.

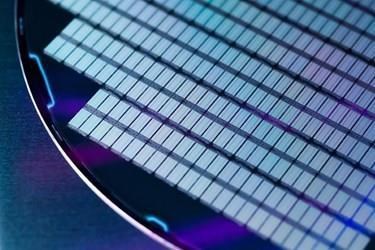

Anche prima che le maschere per processi maturi scendessero di prezzo, una via a basso costo nella prototipazione ASIC e persino nella produzione a basso volume risiedeva nel wafer multi-progetto (MPW) o "navetta", per usare il nome preferito dalla fonderia TSMC. Ciò sfrutta il differenziale tra la dimensione della maggior parte dei circuiti integrati (IC) commerciali e l'area del reticolo che lo strumento di litografia utilizza per stampare le caratteristiche sulla superficie del wafer. Puoi ottenere molti design che occupano da 10 a millimetri quadrati su un reticolo che può misurare 600 millimetri quadrati. D'altra parte, il numero di chip che puoi scegliere di ricevere potrebbe essere limitato a poche dozzine, ma potenzialmente sufficiente per portare un progetto al punto in cui un finanziamento esterno è un'opzione.

Il set di maschere è tutt'altro che l'unico costo di ingegneria iniziale. Gli strumenti e l'IP sono vitali per qualsiasi progetto, che all'estremità superiore può facilmente raggiungere milioni. Un'opzione per i progettisti con pochi soldi risiede negli strumenti a basso costo, come la suite Tanner venduta da Siemens Digital Industries Software e IP. Arm, ad esempio, ha riorganizzato il suo programma DesignStart all'inizio di questo mese, offrendo l'accesso a una selezione dei suoi core orientati al microcontrollore senza richiedere un canone di licenza anticipato, solo royalties dopo la produzione.

Altre attività rispecchiano ciò che è accaduto in molte parti dello sviluppo del software con progetti come Eclipse: costruire un ambiente di progettazione attorno a strumenti open source. Molti team di progettazione di chip stanno già utilizzando in parte l'open source, attraverso il linguaggio di modellazione SystemC e il linguaggio di programmazione Python, che ha trovato il favore di controllare i test harness utilizzati nella verifica RTL.

Iniziative opensource

Un'iniziativa potenzialmente importante è l'iniziativa OpenRoad dell'agenzia di ricerca statunitense DARPA, con l'obiettivo di creare un insieme più completo di strumenti di progettazione open source. Il professor Andrew Kahng dell'Università della California a San Diego e ricercatore principale del progetto prevede un ambiente in grado di disporre e ottimizzare automaticamente una serie di progetti di chip attraverso una combinazione di apprendimento automatico e ciò che lui chiama "partizionamento estremo", che divide il chip in molti piccoli moduli ottimizzati in modo indipendente.

Sebbene gli ingegneri della verifica abbiano abbracciato varie forme di open source, gli ostacoli alla sua adozione aumentano man mano che ci si avvicina al tape-out. Il problema più grande risiede nei kit di progettazione dei processi (PDK) forniti dalle fonderie che sono gelosamente protetti da accordi di non divulgazione e che vietano qualsiasi condivisione.

Figure sopra e sotto: L'infrastruttura di test Caravel, sviluppata da Antmicro, fornisce un anello di I/O e porte di test amministrate da un core RISC-V integrato

"Efabless non è stato in grado di rilasciare un risultato completamente riutilizzabile", osserva Ansell. “Uno come me non ha potuto guardare come qualcosa è stato implementato nei cancelli. C'è un atteggiamento problematico in questo settore riguardo alla condivisione”.

Ansell afferma che Google è entusiasta della capacità di condividere la conoscenza sulla base del fatto che accelera i progressi in generale. "Con il rallentamento della legge di Moore, saranno necessarie nuove soluzioni innovative per tenere il passo con la domanda sempre crescente di calcolo", aggiunge.

Fornire a una comunità più ampia l'accesso alla progettazione del silicio può fornire strade per la creazione di nuovi metodi di calcolo che hanno meno probabilità di derivare dalla tradizionale ricerca e sviluppo. Per aiutare a spingere in avanti, Ansell ha iniziato a cercare di convincere le fonderie ad aprire i loro PDK. “Ho parlato con molte fonderie. E sono stato deriso da molte fonderie”.

Una fonderia ha avuto l'idea: Skywater, un'azienda che gestisce una fabbrica in Minnesota di proprietà di Cypress Semiconductors fino a pochi anni fa. "Siamo riusciti a raggiungere un accordo che ci ha permesso di rilasciare un PDK a 130 nm con una licenza open source", afferma Ansell. Scaricabile da Github, il PDK utilizza una licenza Apache 2.0 e può essere clonato da qualsiasi utente “senza dover chiedere il mio permesso o dover chiedere il permesso a Skywater. Un PDK open source significa che possiamo avere ASIC completamente open source".

Google ed eFabless hanno quindi iniziato a creare un servizio MPW che estendesse la possibilità di progettazione ASIC a persone senza le decine di migliaia di dollari per ottenere qualcosa in cambio dal fab. Per qualificarsi per i chip gratuiti, i progettisti devono essere preparati non solo a realizzare i propri progetti open source, ma devono anche essere preparati a fornire campioni agli utenti interessati a lavorare con il design e il silicio risultante. "Il tuo design deve essere open source fino al GDS", afferma Ansell.

La navetta restituirà circa un centinaio di campioni, che Ansell considera un numero abbastanza alto da consentire agli utenti di non preoccuparsi di fornire ad altri utenti silicio su richiesta e di provare a sfruttare le possibilità di condivisione dell'hardware open source. “L'open source facilita la collaborazione delle persone. Ciò consente alle persone di tentare cose che pensavano fossero troppo rischiose. Rende facile ed economico fallire e imparare dai propri fallimenti”.

vincoli

Un ulteriore vincolo è la necessità di utilizzare l'infrastruttura di test Caravel sviluppata da Antmicro. Ciò fornisce un anello di I/O e porte di test amministrato da un core RISC-V integrato. "Se stai costruendo un chip di prova per cominciare, hai bisogno di qualcosa di simile", osserva il CTO di Efabless e co-fondatore Mohammed Kassem. Al centro di questo anello I/O c'è un foro di 10 millimetri quadrati per il silicio personalizzato dell'utente che può essere utilizzato per qualsiasi cosa senza pagamento.

Sebbene l'area sia relativamente piccola, Ansell afferma che è possibile realizzare progetti digitali complessi poiché i 130 nm possono fornire più di 1.5 milioni di porte. "Le persone sottovalutano enormemente le capacità digitali dei nodi più vecchi perché sono usati principalmente in questi giorni per indirizzare progetti a bassa potenza e analogici", osserva.

Le iscrizioni per la prima corsa a Skywater sul processo a 130 nm si sono chiuse a novembre 2020 e la seconda si chiude a metà giugno, con parti da consegnare da quella seconda corsa ai proprietari del progetto all'inizio di dicembre. Google sta finanziando sei delle navette nel prossimo futuro. Efabless offre anche MPW a pagamento per i team di progettazione che non vogliono impegnarsi nel percorso hardware completamente open source.

La prima navetta includeva progetti di aziende come IBM e Quicklogic.

"Ma la cosa più eccitante è che il 60% dei progettisti non ha mai realizzato un ASIC prima", afferma Ansell. "Il successo del programma SkyWater dimostra che esiste un'enorme domanda di soluzioni aperte e ora abbiamo riscontrato un interesse iniziale da parte di altre fonderie".

Mentre il lavoro sui nodi avanzati spinge i costi di progettazione sempre più in alto, sebbene con potenziali enormi ricompense quando i chip risultanti entrano in produzione, il lavoro all'avanguardia sulla democratizzazione del design può rivelarsi altrettanto importante per guidare il progresso nel settore.