Het democratiseren van chipontwerp

Naarmate het 3nm-procesknooppunt de productiegereedheid nadert, zijn de kosten voor het ontwikkelen van chips ervoor nog een tandje hoger.

Toch is er een groeiende druk om chipontwerp te democratiseren: het naar een grotere gemeenschap van ingenieurs brengen, zowel professioneel als amateur. Dit lijkt misschien een onmogelijke taak, maar de beweging werkt aan veel oudere technologieën die geleidelijk toegankelijker worden.

Het is lang niet zo dramatisch als de wet van Moore voor chips met een hoog volume, maar de leercurve van silicium werkt ook voor volwassen processen, vooral voor de initiële kosten zoals het maken van maskers. Bij de introductie kostte een volledige maskerset voor het 180nm-proces gemakkelijk $ 300,000 en liep op tot meer dan een half miljoen dollar voor 130nm. Vandaag is het beeld heel anders. Het globaal Halfgeleider Uit het brancheonderzoek van de Association bleek dat de prijzen van 180nm maskersets in de afgelopen twee jaar niet meer dan $ 60,000 waren en vaak minder dan $ 80,000 voor 130nm-sets.

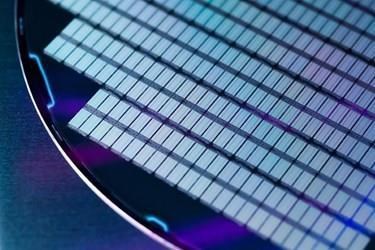

Zelfs voordat volwassen procesmaskers in prijs daalden, lag een goedkope manier om ASIC-prototyping en zelfs productie in kleine volumes in de multi-projectwafer (MPW) of "shuttle" te gebruiken, om de naam te gebruiken die de voorkeur geniet van gieterij TSMC. Dit maakt gebruik van het verschil tussen de grootte van de meeste commerciële geïntegreerde schakelingen (IC's) en het gebied van het dradenkruis dat de lithografietool gebruikt om kenmerken op het oppervlak van de wafer af te drukken. Je kunt veel ontwerpen krijgen die 10 tot vierkante millimeter in beslag nemen op een dradenkruis van wel 600 vierkante millimeter. Aan de andere kant kan het aantal chips dat u kunt ontvangen beperkt zijn tot slechts enkele tientallen, maar potentieel genoeg om een project zover te krijgen dat externe financiering een optie is.

De maskerset is verre van de enige technische kosten vooraf. Tools en IP zijn essentieel voor elk ontwerp, dat aan de bovenkant gemakkelijk in de miljoenen loopt. Een optie voor geldarme ontwerpers ligt in goedkopere tools, zoals de Tanner-suite die wordt verkocht door Siemens Digital Industries Software en IP. Arm heeft bijvoorbeeld eerder deze maand zijn DesignStart-programma aangepast en toegang geboden tot een selectie van zijn microcontroller-georiënteerde kernen zonder voorafgaande licentievergoeding, alleen royalty's na productie.

Andere activiteiten weerspiegelen wat er in veel delen van softwareontwikkeling is gebeurd met projecten zoals Eclipse: een ontwerpomgeving bouwen rond open-sourcetools. Veel chipontwerpteams gebruiken al gedeeltelijk open source, via de modelleertaal SystemC en de programmeertaal Python, die de voorkeur heeft gekregen voor het controleren van de testharnassen die worden gebruikt bij RTL-verificatie.

Opensource-initiatieven

Een potentieel belangrijk initiatief is het OpenRoad-initiatief van het Amerikaanse onderzoeksbureau DARPA, met als doel een uitgebreidere set open-source ontwerptools te bouwen. Professor Andrew Kahng van de Universiteit van Californië in San Diego en hoofdonderzoeker van het project stelt een omgeving voor die een reeks chipontwerpen automatisch kan ontwerpen en afstemmen door een combinatie van machine learning en wat hij "extreme partitionering" noemt, die de chip in vele kleine onafhankelijk geoptimaliseerde modules.

Hoewel verificatie-ingenieurs verschillende vormen van open source hebben omarmd, worden de struikelblokken voor de acceptatie groter naarmate je dichter bij tape-out komt. Het grootste probleem ligt in de procesontwerpkits (PDK's) die worden geleverd door gieterijen die angstvallig worden beschermd door geheimhoudingsovereenkomsten en die het delen ervan verbieden.

Figuren boven en onder: De Caravel-testinfrastructuur, ontwikkeld door Antmicro, biedt een ring van I/O en testpoorten die worden beheerd door een ingebouwde RISC-V-kern

"Efabless kon geen volledig herbruikbaar resultaat vrijgeven", merkt Ansell op. “Iemand als ik kon niet zien hoe iets in de poorten werd geïmplementeerd. Er is een problematische houding in deze industrie rond delen.”

Ansell zegt dat Google enthousiast is over de mogelijkheid om kennis te delen omdat het de vooruitgang in het algemeen versnelt. "Met de vertraging van de wet van Moore zullen nieuwe innovatieve oplossingen nodig zijn om de steeds groeiende vraag naar berekeningen bij te houden", voegt hij eraan toe.

Door een bredere gemeenschap toegang te geven tot siliciumontwerp, kan dit mogelijkheden bieden voor het creëren van nieuwe berekeningsmethoden die minder snel tot stand komen via traditionele R&D. Om dat vooruit te helpen, begon Ansell gieterijen te overtuigen om hun PDK's open te stellen. “Ik heb veel gieterijen gesproken. En ik werd uitgelachen door veel gieterijen.”

Eén gieterij kwam op het idee: Skywater, een bedrijf dat tot een paar jaar geleden een fabriek exploiteert in Minnesota die eigendom was van Cypress Semiconductors. "We zijn erin geslaagd om een overeenkomst te sluiten waardoor we een 130nm PDK konden vrijgeven onder een open-sourcelicentie", zegt Ansell. De PDK kan worden gedownload van Github en gebruikt een Apache 2.0-licentie en kan door elke gebruiker worden gekloond “zonder mijn toestemming te hoeven vragen of toestemming van Skywater te hoeven vragen. Een open-source PDK betekent dat we volledig open-source ASIC's kunnen hebben.”

Google en eFabless begonnen toen met het bouwen van een MPW-service die de mogelijkheid van ASIC-ontwerp uitbreidt tot mensen zonder de tienduizenden dollars om iets terug te krijgen van de fab. Om in aanmerking te komen voor de gratis chips, moeten ontwerpers bereid zijn om niet alleen hun eigen ontwerpen open source te maken, ze moeten ook bereid zijn om monsters te leveren aan gebruikers die geïnteresseerd zijn in het werken met het ontwerp en het resulterende silicium. "Je ontwerp moet open source zijn tot aan de GDS", zegt Ansell.

De shuttle zal ongeveer honderd samples retourneren, wat volgens Ansell hoog genoeg is voor gebruikers om zich geen zorgen te maken over het leveren van silicium aan andere gebruikers op verzoek en om te proberen de deelmogelijkheden van open-source hardware te benutten. “Open source maakt het makkelijk voor mensen om samen te werken. Hierdoor kunnen mensen dingen proberen waarvan ze dachten dat ze te riskant waren. Het maakt het gemakkelijk en goedkoop om te falen en om van je fouten te leren.”

beperkingen

Een andere beperking is de eis om de door Antmicro ontwikkelde Caravel-testinfrastructuur te gebruiken. Dit biedt een ring van I/O- en testpoorten die worden beheerd door een ingebouwde RISC-V-kern. "Als je om te beginnen een testchip bouwt, heb je zoiets nodig", merkt Efabless CTO en mede-oprichter Mohammed Kassem op. In het midden van deze I/O-ring zit een gat van 10 vierkante millimeter voor het door de gebruiker aangepaste silicium dat voor alles kan worden gebruikt zonder te betalen.

Hoewel het gebied relatief klein is, zegt Ansell dat complexe digitale ontwerpen haalbaar zijn, aangezien de 130nm meer dan 1.5 miljoen poorten kan leveren. "Mensen onderschatten de digitale mogelijkheden van oudere nodes enorm, omdat ze tegenwoordig vooral worden gebruikt voor low-power en analoge ontwerpen", merkt hij op.

De inzendingen voor de eerste run bij Skywater op het 130nm-proces sloten in november 2020 en de tweede sluit voor inzendingen medio juni, waarbij onderdelen van die tweede run begin december aan de projecteigenaren moeten worden geleverd. Google financiert in de nabije toekomst zes van de shuttles. Efabless biedt ook betaalde MPW aan ontwerpteams die zich niet willen binden aan de volledig open-source hardwareroute.

De eerste shuttle bevatte ontwerpen van bedrijven als IBM en Quicklogic.

"Maar het meest opwindende was dat 60 procent van de ontwerpers nog nooit een ASIC heeft gedaan", zegt Ansell. "Het succes van het SkyWater-programma laat zien dat er een enorme vraag is naar open oplossingen en dat we nu ook de eerste interesse hebben gekregen van andere gieterijen."

Terwijl het werken aan geavanceerde knooppunten de ontwerpkosten steeds hoger opdrijft, hoewel met potentieel enorme beloningen wanneer de resulterende chips in productie gaan, kan het werken aan de achterhoede aan het democratiseren van ontwerp even belangrijk zijn om vooruitgang in de industrie te stimuleren.