การออกแบบชิปที่เป็นประชาธิปไตย

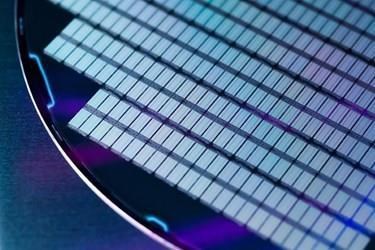

เนื่องจากโหนดกระบวนการ 3nm ใกล้ความพร้อมในการผลิต ต้นทุนในการพัฒนาชิปสำหรับโหนดนั้นจึงเพิ่มขึ้นอีกระดับหนึ่ง

ทว่ายังมีแรงผลักดันมากขึ้นเรื่อยๆ ในการออกแบบชิปให้เป็นประชาธิปไตย: นำไปสู่ชุมชนวิศวกรในวงกว้างขึ้น ทั้งมืออาชีพและมือสมัครเล่น นี้อาจดูเหมือนเป็นงานที่เป็นไปไม่ได้ แต่การเคลื่อนไหวกำลังทำงานกับเทคโนโลยีที่เก่ากว่ามากในขณะที่พวกเขาค่อยๆเข้าถึงได้มากขึ้น

ไม่มีที่ไหนที่ใกล้ดราม่าเท่ากฎของมัวร์สำหรับชิปที่มีปริมาณมาก แต่เส้นโค้งการเรียนรู้ของซิลิกอนก็ใช้ได้กับกระบวนการที่โตเต็มที่เช่นกัน โดยเฉพาะอย่างยิ่งสำหรับค่าใช้จ่ายล่วงหน้า เช่น การทำหน้ากาก ในช่วงแนะนำ ชุดมาสก์แบบเต็มสำหรับกระบวนการ 180nm อาจมีราคา 300,000 ดอลลาร์และวิ่งไปมากกว่าครึ่งล้านดอลลาร์สำหรับ 130 นาโนเมตร วันนี้ภาพค่อนข้างแตกต่าง The Global สารกึ่งตัวนำ การสำรวจอุตสาหกรรมของสมาคมพบว่าในช่วงสองปีที่ผ่านมา ราคาชุดหน้ากาก 180nm ไม่เกิน 60,000 ดอลลาร์ และมักจะต่ำกว่า 80,000 ดอลลาร์สำหรับชุด 130 นาโนเมตร

แม้กระทั่งก่อนที่มาสก์แปรรูปจะลดราคาลง วิธีการหนึ่งที่มีต้นทุนต่ำในการสร้างต้นแบบของ ASIC และแม้แต่การผลิตในปริมาณน้อยก็อยู่ในเวเฟอร์หลายโครงการ (MPW) หรือ "รถรับส่ง" เพื่อใช้ชื่อที่โรงหล่อ TSMC ชื่นชอบ สิ่งนี้ใช้ประโยชน์จากความแตกต่างระหว่างขนาดของวงจรรวมเชิงพาณิชย์ (IC) ส่วนใหญ่กับพื้นที่ของเส้นเล็งที่เครื่องมือการพิมพ์หินใช้เพื่อพิมพ์คุณสมบัติบนพื้นผิวของเวเฟอร์ คุณสามารถออกแบบได้มากซึ่งกินพื้นที่ตั้งแต่ 10 ถึงตารางมิลลิเมตรบนเส้นเล็งที่อาจวัดได้ 600 ตารางมิลลิเมตร ในทางกลับกัน จำนวนชิปที่คุณสามารถเลือกรับได้อาจถูกจำกัดเพียงไม่กี่โหล แต่อาจเพียงพอที่จะทำให้โครงการไปถึงจุดที่เงินทุนภายนอกเป็นตัวเลือก

ชุดหน้ากากอยู่ไกลจากต้นทุนทางวิศวกรรมล่วงหน้าเพียงอย่างเดียว เครื่องมือและ IP มีความสำคัญสำหรับการออกแบบใดๆ ซึ่งในระดับสูงอาจมีจำนวนนับล้านได้อย่างง่ายดาย ทางเลือกหนึ่งสำหรับนักออกแบบที่ขาดแคลนเงินสดคือเครื่องมือที่มีต้นทุนต่ำ เช่น ชุด Tanner ที่จำหน่ายโดย Siemens Digital Industries Software และ IP ตัวอย่างเช่น Arm ได้ทำการ rejigged โปรแกรม DesignStart เมื่อต้นเดือนนี้ โดยเสนอการเข้าถึงคอร์ที่เน้นไมโครคอนโทรลเลอร์ที่ได้รับการคัดสรรโดยไม่ต้องเสียค่าธรรมเนียมใบอนุญาตล่วงหน้า เพียงค่าลิขสิทธิ์หลังการผลิต

กิจกรรมอื่นๆ สะท้อนสิ่งที่เกิดขึ้นในหลายส่วนของการพัฒนาซอฟต์แวร์ด้วยโครงการต่างๆ เช่น Eclipse: สร้างสภาพแวดล้อมการออกแบบรอบเครื่องมือโอเพนซอร์ซ ทีมออกแบบชิปจำนวนมากใช้โอเพ่นซอร์สในบางส่วนแล้ว ผ่านภาษาการสร้างแบบจำลอง SystemC เช่นเดียวกับภาษาโปรแกรม Python ซึ่งพบว่าชอบการควบคุมสายรัดทดสอบที่ใช้ในการตรวจสอบ RTL

ความคิดริเริ่มของโอเพ่นซอร์ส

ความคิดริเริ่มที่สำคัญที่อาจเป็นไปได้คือความคิดริเริ่ม OpenRoad ของหน่วยงานวิจัยของสหรัฐอเมริกา DARPA โดยมีเป้าหมายเพื่อสร้างชุดเครื่องมือการออกแบบโอเพนซอร์ซที่ครอบคลุมมากขึ้น ศาสตราจารย์แอนดรูว์ แคงแห่งมหาวิทยาลัยแคลิฟอร์เนีย ซานดิเอโก และผู้ตรวจสอบหลักของโครงการ มองเห็นสภาพแวดล้อมที่สามารถจัดวางและปรับแต่งการออกแบบชิปต่างๆ ได้โดยอัตโนมัติผ่านการผสมผสานระหว่างการเรียนรู้ของเครื่องและสิ่งที่เขาเรียกว่า "การแบ่งพาร์ติชันขั้นสุด" ซึ่งแบ่ง ชิปลงในโมดูลที่ปรับให้เหมาะสมขนาดเล็กจำนวนมาก

แม้ว่าวิศวกรด้านการตรวจสอบความถูกต้องจะใช้โอเพ่นซอร์สในรูปแบบต่างๆ แต่อุปสรรคในการนำไปใช้นั้นยิ่งใหญ่ขึ้นเมื่อคุณเข้าใกล้เทปมากขึ้น ปัญหาที่ใหญ่ที่สุดอยู่ในชุดการออกแบบกระบวนการ (PDK) ที่จัดหาโดยโรงหล่อที่ได้รับการคุ้มครองอย่างอิจฉาริษยาโดยข้อตกลงไม่เปิดเผยข้อมูลและห้ามไม่ให้มีการแบ่งปัน

รูปด้านบนและด้านล่าง: โครงสร้างพื้นฐานการทดสอบของ Caravel ที่พัฒนาโดย Antmicro มีวงแหวนของ I/O และพอร์ตทดสอบที่ควบคุมโดยแกน RISC-V ในตัว

“Efabless ไม่สามารถปล่อยผลลัพธ์ที่นำกลับมาใช้ใหม่ได้อย่างสมบูรณ์” Ansell ตั้งข้อสังเกต “คนอย่างฉันมองไม่เห็นว่ามีบางอย่างเกิดขึ้นที่ประตูอย่างไร มีทัศนคติที่เป็นปัญหาในอุตสาหกรรมนี้เกี่ยวกับการแบ่งปัน”

Ansell กล่าวว่า Google กระตือรือร้นที่จะแบ่งปันความรู้บนพื้นฐานที่จะช่วยเร่งความก้าวหน้าโดยทั่วไป “ด้วยกฎหมายของมัวร์ที่ชะลอความเร็วของโซลูชั่นที่เป็นนวัตกรรมใหม่ จำเป็นเพื่อให้ทันกับความต้องการด้านการคำนวณที่เพิ่มขึ้นเรื่อยๆ” เขากล่าวเสริม

การให้ชุมชนในวงกว้างเข้าถึงการออกแบบซิลิกอนอาจเป็นหนทางสำหรับการสร้างวิธีการใหม่ ๆ สำหรับการคำนวณที่ไม่น่าจะเกิดขึ้นจากการวิจัยและพัฒนาแบบเดิม เพื่อช่วยผลักดันสิ่งนั้น Ansell เริ่มพยายามโน้มน้าวให้โรงหล่อเปิด PDK ของพวกเขา “ฉันได้พูดคุยกับโรงหล่อจำนวนมาก และฉันก็ถูกหัวเราะเยาะจากโรงหล่อมากมาย”

โรงหล่อแห่งหนึ่งเกิดแนวคิดขึ้น: Skywater ซึ่งเป็นบริษัทที่ดำเนินการโรงงานในมินนิโซตาซึ่งเป็นเจ้าของโดย Cypress Semiconductors เมื่อไม่กี่ปีที่ผ่านมา “เราสามารถบรรลุข้อตกลงที่อนุญาตให้เราปล่อย 130nm PDK ภายใต้ใบอนุญาตโอเพนซอร์ส” Ansell กล่าว ดาวน์โหลดได้จาก Github PDK ใช้ใบอนุญาต Apache 2.0 และสามารถโคลนได้โดยผู้ใช้ทุกคน "โดยไม่ต้องขออนุญาตจากฉันหรือต้องขออนุญาตจาก Skywater PDK แบบโอเพ่นซอร์สหมายความว่าเราสามารถมี ASIC แบบโอเพ่นซอร์สได้อย่างเต็มที่”

จากนั้น Google และ eFabless ก็เริ่มสร้างบริการ MPW ที่ขยายความเป็นไปได้ของการออกแบบ ASIC ให้กับผู้ที่ไม่มีเงินหลายหมื่นดอลลาร์เพื่อรับบางสิ่งกลับมาจาก fab เพื่อให้มีคุณสมบัติสำหรับชิปฟรี นักออกแบบต้องเตรียมพร้อมที่จะไม่เพียงแค่สร้างโอเพ่นซอร์สสำหรับการออกแบบของตนเองเท่านั้น แต่ยังต้องเตรียมส่งตัวอย่างไปยังผู้ใช้ที่สนใจจะทำงานกับการออกแบบและผลลัพธ์ของซิลิคอนด้วย "การออกแบบของคุณต้องเป็นโอเพ่นซอร์สไปจนถึง GDS" Ansell กล่าว

รถรับส่งจะส่งกลับตัวอย่างประมาณ XNUMX ตัวอย่าง ซึ่ง Ansell มองว่าเป็นจำนวนที่เพียงพอสำหรับผู้ใช้โดยไม่ต้องกังวลกับการให้ซิลิคอนกับผู้ใช้รายอื่นตามคำขอ และพยายามนำเสนอความเป็นไปได้ในการแบ่งปันของฮาร์ดแวร์โอเพนซอร์ส “โอเพ่นซอร์สทำให้ผู้คนทำงานร่วมกันได้ง่าย วิธีนี้ทำให้ผู้คนได้ลองทำในสิ่งที่พวกเขาเคยคิดว่าเสี่ยงเกินไป มันทำให้ง่ายและราคาถูกที่จะล้มเหลว และเรียนรู้จากความล้มเหลวของคุณ”

ข้อ จำกัด

ข้อจำกัดเพิ่มเติมคือข้อกำหนดในการใช้โครงสร้างพื้นฐานการทดสอบของ Caravel ที่พัฒนาโดย Antmicro ซึ่งให้วงแหวนของ I/O และพอร์ตทดสอบที่ควบคุมโดยแกน RISC-V ในตัว “หากคุณกำลังสร้างชิปทดสอบตั้งแต่แรก คุณต้องมีสิ่งนี้” Efabless CTO และผู้ร่วมก่อตั้ง Mohammed Kassem กล่าว ตรงกลางของวงแหวน I/O นี้คือรูขนาด 10 มม. สำหรับซิลิกอนแบบกำหนดเองของผู้ใช้ ซึ่งสามารถใช้ทำอะไรก็ได้โดยไม่ต้องจ่ายเงิน

แม้ว่าพื้นที่จะค่อนข้างเล็ก Ansell กล่าวว่าการออกแบบดิจิทัลที่ซับซ้อนสามารถทำได้ เนื่องจาก 130nm สามารถส่งได้มากกว่า 1.5 ล้านเกท “ผู้คนประเมินความสามารถทางดิจิทัลของโหนดรุ่นเก่าต่ำไปอย่างมาก เนื่องจากปัจจุบันส่วนใหญ่ใช้โหนดเหล่านี้เพื่อกำหนดเป้าหมายการออกแบบที่ใช้พลังงานต่ำและอนาล็อก” เขากล่าว

การส่งงานครั้งแรกที่ Skywater ในกระบวนการ 130nm ปิดในเดือนพฤศจิกายน 2020 และครั้งที่สองจะปิดการส่งในช่วงกลางเดือนมิถุนายน โดยชิ้นส่วนต่างๆ จะจัดส่งจากการวิ่งครั้งที่สองไปยังเจ้าของโครงการในต้นเดือนธันวาคม Google กำลังระดมทุนสำหรับรถรับส่งจำนวน XNUMX ลำในอนาคตอันใกล้นี้ Efabless ยังเสนอ MPW แบบชำระเงินสำหรับทีมออกแบบที่ไม่ต้องการผูกมัดกับเส้นทางฮาร์ดแวร์โอเพนซอร์ซทั้งหมด

รถรับส่งคันแรกรวมการออกแบบจากบริษัทต่างๆ เช่น IBM และ Quicklogic

“แต่สิ่งที่น่าตื่นเต้นที่สุดคือ 60% ของนักออกแบบไม่เคยทำ ASIC มาก่อน” Ansell กล่าว “ความสำเร็จของโครงการ SkyWater แสดงให้เห็นว่ามีความต้องการโซลูชั่นแบบเปิดจำนวนมาก และตอนนี้เราก็ได้รับความสนใจจากโรงหล่ออื่นๆ ในเบื้องต้นแล้ว”

แม้ว่าการทำงานกับโหนดขั้นสูงจะทำให้ต้นทุนการออกแบบสูงขึ้น แม้ว่าจะมีผลตอบแทนมหาศาลเมื่อชิปที่ได้เข้าสู่กระบวนการผลิต การทำงานที่ขอบท้ายในการออกแบบที่เป็นประชาธิปไตยอาจพิสูจน์ได้ว่ามีความสำคัญเท่าเทียมกันในการขับเคลื่อนความก้าวหน้าในอุตสาหกรรม