Democratizando o design do chip

À medida que o nó de processo de 3 nm se aproxima da prontidão para produção, o custo de desenvolvimento de chips para ele subiu mais um degrau.

No entanto, há um impulso crescente para democratizar o design de chips: trazendo-os para uma comunidade mais ampla de engenheiros, profissionais e amadores. Isso pode parecer uma tarefa impossível, mas o movimento está trabalhando em tecnologias muito mais antigas à medida que se tornam mais acessíveis.

Não é nem de longe tão dramático quanto a Lei de Moore para chips de alto volume, mas a curva de aprendizado do silício também funciona para processos maduros, especialmente para os custos iniciais, como fabricação de máscaras. Na introdução, um conjunto de máscara completa para o processo de 180 nm pode facilmente custar US $ 300,000 e chegar a mais de meio milhão de dólares por 130 nm. Hoje o quadro é bem diferente. O global Semicondutores A pesquisa do setor da Association revelou que, nos últimos dois anos, os preços dos conjuntos de máscaras de 180 nm não eram mais do que US $ 60,000 e geralmente abaixo de US $ 80,000 para conjuntos de 130 nm.

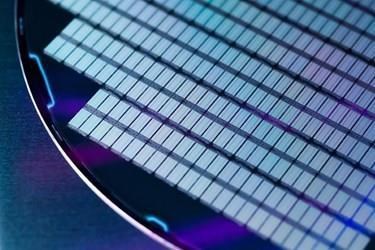

Mesmo antes de as máscaras de processos maduros caírem de preço, uma maneira de baixo custo para a prototipagem ASIC e até mesmo para a fabricação de baixo volume era o wafer multiprojeto (MPW) ou “shuttle”, para usar o nome preferido pela fundição TSMC. Isso tira vantagem do diferencial entre o tamanho da maioria dos circuitos integrados (ICs) comerciais e a área do retículo que a ferramenta de litografia usa para imprimir recursos na superfície do wafer. Você pode obter muitos designs que ocupam de 10 a milímetros quadrados em um retículo que pode medir 600 milímetros quadrados. Por outro lado, o número de fichas que você pode optar por receber pode ser limitado a apenas algumas dezenas, mas potencialmente o suficiente para levar um projeto ao ponto em que o financiamento externo é uma opção.

O conjunto de máscaras está longe de ser o único custo inicial de engenharia. Ferramentas e IP são vitais para qualquer projeto, que na extremidade superior chega facilmente a milhões. Uma opção para designers com pouco dinheiro reside em ferramentas de custo mais baixo, como o pacote Tanner vendido pela Siemens Digital Industries Software e IP. A Arm, por exemplo, reformulou seu programa DesignStart no início deste mês, oferecendo acesso a uma seleção de seus núcleos orientados para microcontroladores sem exigir uma taxa de licença inicial, apenas royalties após a produção.

Outras atividades espelham o que aconteceu em muitas partes do desenvolvimento de software com projetos como o Eclipse: construir um ambiente de design em torno de ferramentas de código aberto. Muitas equipes de design de chips já estão usando código aberto em parte, por meio da linguagem de modelagem SystemC, bem como da linguagem de programação Python, que encontrou preferência para controlar os chicotes de teste usados na verificação RTL.

Iniciativas de código aberto

Uma iniciativa potencialmente importante é a iniciativa OpenRoad da agência de pesquisa dos EUA DARPA, com o objetivo de construir um conjunto mais abrangente de ferramentas de design de código aberto. O professor Andrew Kahng, da Universidade da Califórnia em San Diego e principal investigador do projeto, prevê um ambiente que pode definir e ajustar uma variedade de designs de chips automaticamente por meio de uma combinação de aprendizado de máquina e o que ele chama de "particionamento extremo", que divide o chip em muitos pequenos módulos otimizados de forma independente.

Embora os engenheiros de verificação tenham adotado várias formas de código aberto, os obstáculos para sua adoção ficam maiores quanto mais perto você chega da fita. O maior problema reside nos kits de design de processo (PDKs) fornecidos por fundições que são zelosamente protegidas por acordos de não divulgação e que proíbem qualquer compartilhamento.

Figuras acima e abaixo: A infraestrutura de teste Caravel, desenvolvida pela Antmicro, fornece um anel de E / S e portas de teste administradas por um núcleo RISC-V integrado

“Efabless não conseguiu liberar um resultado completamente reutilizável”, observa Ansell. “Alguém como eu não conseguia ver como algo foi implementado nos portões. Há uma atitude problemática nesta indústria em torno do compartilhamento ”.

Ansell diz que o Google está interessado na capacidade de compartilhar conhecimento com base no fato de que isso acelera o progresso em geral. “Com a lei de Moore desacelerando, novas soluções inovadoras serão necessárias para acompanhar a crescente demanda por computação”, acrescenta.

Fornecer a uma comunidade mais ampla acesso ao design de silício pode fornecer caminhos para a criação de novos métodos de computação que são menos prováveis de surgir por meio de P&D tradicional. Para ajudar a levar isso adiante, a Ansell começou a tentar convencer as fundições a abrir seus PDKs. “Conversei com muitas fundições. E muitas fundições riram de mim. ”

Uma fundição aceitou a ideia: a Skywater, uma empresa que operava uma fábrica em Minnesota de propriedade da Cypress Semiconductors até alguns anos atrás. “Conseguimos chegar a um acordo que nos permitiu lançar um PDK de 130 nm sob uma licença de código aberto”, diz Ansell. Pode ser baixado do Github, o PDK usa uma licença Apache 2.0 e pode ser clonado por qualquer usuário “sem ter que pedir minha permissão ou ter que pedir permissão da Skywater. Um PDK de código aberto significa que podemos ter ASICs totalmente de código aberto. ”

O Google e a eFabless então começaram a construir um serviço MPW que estende a possibilidade de design ASIC para pessoas sem as dezenas de milhares de dólares para obter algo em troca da fábrica. Para se qualificar para os chips gratuitos, os designers precisam estar preparados não apenas para fazer seus próprios designs de código aberto, mas também para entregar amostras aos usuários interessados em trabalhar com o design e o silício resultante. “Seu design deve ser de código aberto até o GDS”, diz Ansell.

O ônibus espacial retornará cerca de cem amostras, que a Ansell vê como um número alto o suficiente para que os usuários não se preocupem em fornecer silício a outros usuários mediante solicitação e tentem oferecer as possibilidades de compartilhamento do hardware de código aberto. “O código aberto facilita a colaboração das pessoas. Isso permite que as pessoas tentem coisas que costumavam pensar que eram muito arriscadas. Torna mais fácil e barato fracassar e aprender com seus fracassos. ”

restrições

Uma outra restrição é a necessidade de usar a infraestrutura de teste do Caravel desenvolvida pela Antmicro. Isso fornece um anel de portas de E / S e teste administrado por um núcleo RISC-V integrado. “Se você está construindo um chip de teste para começar, você precisa de algo assim”, observa Efabless CTO e co-fundador Mohammed Kassem. No meio desse anel de E / S está um orifício de 10 milímetros quadrados para o silicone personalizado do usuário, que pode ser usado para qualquer coisa sem pagamento.

Embora a área seja relativamente pequena, Ansell diz que projetos digitais complexos são alcançáveis, já que o 130nm pode entregar mais de 1.5 milhão de portas. “As pessoas subestimam enormemente as capacidades digitais de nós mais antigos porque eles são usados principalmente hoje em dia para atingir projetos analógicos e de baixa potência”, observa ele.

As inscrições para a primeira execução na Skywater no processo de 130 nm encerradas em novembro de 2020 e a segunda fecha para inscrições em meados de junho, com peças a serem entregues a partir dessa segunda execução para os proprietários do projeto no início de dezembro. O Google está financiando seis dos ônibus em um futuro próximo. Efabless também oferece MPW pago para equipes de design que não querem se comprometer com a rota de hardware totalmente de código aberto.

O primeiro transporte incluiu projetos de empresas como IBM e Quicklogic.

“Mas o mais empolgante é que 60% dos designers nunca fizeram um ASIC antes”, diz Ansell. “O sucesso do programa SkyWater mostra que existe uma grande demanda por soluções abertas e agora tivemos algum interesse inicial de outras fundições.”

Embora o trabalho em nós avançados empurre os custos de design ainda mais para cima, embora com recompensas potencialmente enormes quando os chips resultantes entrarem em produção, trabalhar na vanguarda da democratização do design pode ser igualmente importante para impulsionar o progresso na indústria.