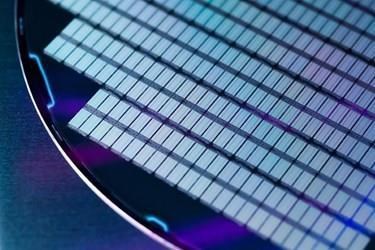

Democratizar el diseño de chips

A medida que el nodo de proceso de 3 nm se acerca a la preparación de producción, el costo de desarrollar chips para él ha subido otro nivel.

Sin embargo, existe un impulso creciente para democratizar el diseño de chips: llevarlo a una comunidad más amplia de ingenieros, tanto profesionales como aficionados. Esto puede parecer una tarea imposible, pero el movimiento está trabajando en tecnologías mucho más antiguas a medida que gradualmente se vuelven más accesibles.

No es tan dramático como la Ley de Moore para chips de alto volumen, pero la curva de aprendizaje del silicio también funciona para procesos maduros, particularmente para los costos iniciales, como la fabricación de máscaras. En la introducción, un conjunto completo de máscaras para el proceso de 180 nm podría costar fácilmente $ 300,000 y llegar a más de medio millón de dólares por 130 nm. Hoy el panorama es bastante diferente. Lo global Semiconductores La encuesta de la industria de la Asociación descubrió en los últimos dos años que los precios de los juegos de mascarillas de 180 nm no superaban los $ 60,000 y, a menudo, estaban por debajo de los $ 80,000 para los juegos de 130 nm.

Incluso antes de que las máscaras de proceso maduro bajaran de precio, una forma de bajo costo en la creación de prototipos ASIC e incluso en la fabricación de bajo volumen consistía en la oblea multiproyecto (MPW) o "lanzadera", para usar el nombre preferido por la fundición TSMC. Esto aprovecha la diferencia entre el tamaño de la mayoría de los circuitos integrados comerciales (CI) y el área del retículo que utiliza la herramienta de litografía para imprimir características en la superficie de la oblea. Puede obtener muchos diseños que ocupan de 10 a milímetros cuadrados en una retícula que puede medir 600 milímetros cuadrados. Por otro lado, la cantidad de chips que puede optar por recibir puede estar limitada a solo unas pocas docenas, pero potencialmente suficiente para llevar un proyecto al punto en que la financiación externa sea una opción.

El conjunto de máscaras está lejos de ser el único costo de ingeniería inicial. Las herramientas y la propiedad intelectual son vitales para cualquier diseño, que en el extremo superior puede llegar a millones. Una opción para los diseñadores con escasez de efectivo radica en herramientas de menor costo, como la suite Tanner vendida por Siemens Digital Industries Software and IP. Arm, por ejemplo, reajustó su programa DesignStart a principios de este mes, ofreciendo acceso a una selección de sus núcleos orientados a microcontroladores sin exigir una tarifa de licencia por adelantado, solo regalías después de la producción.

Otras actividades reflejan lo que ha sucedido en muchas partes del desarrollo de software con proyectos como Eclipse: construir un entorno de diseño en torno a herramientas de código abierto. Muchos equipos de diseño de chips ya están utilizando el código abierto en parte, a través del lenguaje de modelado SystemC, así como el lenguaje de programación Python, que ha encontrado favor para controlar los arneses de prueba utilizados en la verificación RTL.

Iniciativas de código abierto

Una iniciativa potencialmente importante es la iniciativa OpenRoad de la agencia de investigación estadounidense DARPA, cuyo objetivo es crear un conjunto más completo de herramientas de diseño de código abierto. El profesor Andrew Kahng de la Universidad de California en San Diego e investigador principal del proyecto prevé un entorno que puede diseñar y ajustar una variedad de diseños de chips automáticamente a través de una combinación de aprendizaje automático y lo que él llama "partición extrema", que divide el chip en muchos pequeños módulos optimizados de forma independiente.

Aunque los ingenieros de verificación han adoptado varias formas de código abierto, los obstáculos para su adopción se hacen más grandes cuanto más se acerca a la cinta. El mayor problema radica en los kits de diseño de procesos (PDK) proporcionados por las fundiciones que están celosamente protegidos por acuerdos de confidencialidad y que prohíben cualquier intercambio.

Figuras arriba y abajo: La infraestructura de prueba Caravel, desarrollada por Antmicro, proporciona un anillo de E / S y puertos de prueba administrados por un núcleo RISC-V incorporado

"Efabless no pudo publicar un resultado completamente reutilizable", señala Ansell. “Alguien como yo no podía ver cómo se implementó algo en las puertas. Hay una actitud problemática en esta industria en torno al intercambio ".

Ansell dice que Google está interesado en la capacidad de compartir conocimientos sobre la base de que acelera el progreso en general. “Con la ley de Moore ralentizándose, se necesitarán nuevas soluciones innovadoras para mantenerse al día con la creciente demanda de computación”, agrega.

Proporcionar acceso al diseño de silicio a una comunidad más amplia puede proporcionar vías para crear métodos novedosos de computación que es menos probable que surjan a través de la I + D tradicional. Para ayudar a impulsar eso, Ansell comenzó a tratar de convencer a las fundiciones para que abrieran sus PDK. “Hablé con muchas fundiciones. Y muchas fundiciones se rieron de mí ".

Una fundición se le ocurrió la idea: Skywater, una empresa que operaba una fábrica en Minnesota propiedad de Cypress Semiconductors hasta hace unos años. “Pudimos llegar a un acuerdo que nos permitió lanzar un PDK de 130 nm con una licencia de código abierto”, dice Ansell. Descargable desde Github, el PDK usa una licencia Apache 2.0 y puede ser clonado por cualquier usuario “sin tener que pedir mi permiso o tener que pedir permiso a Skywater. Un PDK de código abierto significa que podemos tener ASIC de código abierto ".

Luego, Google y eFabless se propusieron construir un servicio MPW que amplíe la posibilidad de diseño ASIC a personas sin decenas de miles de dólares para obtener algo a cambio de la fábrica. Para calificar para los chips gratuitos, los diseñadores deben estar preparados no solo para hacer sus propios diseños de código abierto, sino que también deben estar preparados para entregar muestras a los usuarios que estén interesados en trabajar con el diseño y el silicio resultante. “Su diseño tiene que ser de código abierto hasta el GDS”, dice Ansell.

El transbordador devolverá alrededor de un centenar de muestras, lo que Ansell considera un número lo suficientemente alto como para que los usuarios no se preocupen por proporcionar silicio a otros usuarios a pedido y tratar de cumplir con las posibilidades de uso compartido del hardware de código abierto. “El código abierto facilita la colaboración de las personas. Esto permite a las personas intentar cosas que solían pensar que eran demasiado riesgosas. Hace que fallar sea fácil y barato, y aprender de sus fallas ".

Limitaciones

Otra limitación es el requisito de utilizar la infraestructura de prueba Caravel desarrollada por Antmicro. Esto proporciona un anillo de puertos de prueba y E / S administrados por un núcleo RISC-V integrado. "Si está construyendo un chip de prueba para empezar, necesita algo como esto", señala el CTO y cofundador de Efabless, Mohammed Kassem. En el medio de este anillo de E / S hay un orificio de 10 milímetros cuadrados para el silicio personalizado del usuario que se puede usar para cualquier cosa sin pago.

Aunque el área es relativamente pequeña, Ansell dice que se pueden lograr diseños digitales complejos ya que el 130nm puede entregar más de 1.5 millones de puertas. "La gente subestima enormemente las capacidades digitales de los nodos más antiguos porque se utilizan principalmente en estos días para apuntar a diseños analógicos y de bajo consumo", señala.

Las presentaciones para la primera ejecución en Skywater en el proceso de 130 nm se cerraron en noviembre de 2020 y la segunda se cierra para presentaciones a mediados de junio, y las piezas se entregarán a partir de esa segunda ejecución a los propietarios del proyecto a principios de diciembre. Google está financiando seis de los transbordadores en un futuro próximo. Efabless también ofrece MPW de pago para los equipos de diseño que no quieren comprometerse con la ruta del hardware de código abierto.

El primer transbordador incluyó diseños de empresas como IBM y Quicklogic.

“Pero lo más emocionante fue que el 60 por ciento de los diseñadores nunca antes había hecho un ASIC”, dice Ansell. "El éxito del programa SkyWater muestra que existe una gran demanda de soluciones abiertas y ahora hemos tenido un interés inicial de otras fundiciones".

Si bien el trabajo en nodos avanzados aumenta los costos de diseño, aunque con recompensas potencialmente enormes cuando los chips resultantes entran en producción, el trabajo en la vanguardia de la democratización del diseño puede resultar igualmente importante para impulsar el progreso en la industria.