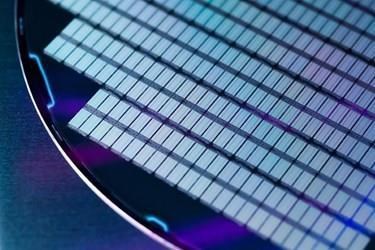

칩 설계 민주화

3nm 공정 노드가 생산 준비 상태에 가까워짐에 따라 이를 위한 칩 개발 비용이 한 단계 더 높아졌습니다.

그러나 칩 설계를 민주화하려는 노력이 점점 더 커지고 있습니다. 즉, 전문가와 아마추어 모두를 포함한 더 넓은 엔지니어 커뮤니티에 이를 제공하는 것입니다. 이는 불가능한 작업처럼 보일 수 있지만 점차적으로 접근성이 높아짐에 따라 훨씬 더 오래된 기술에 대한 운동이 진행되고 있습니다.

대용량 칩에 대한 무어의 법칙만큼 극적이지는 않지만 실리콘 학습 곡선은 성숙한 프로세스, 특히 마스크 제작과 같은 초기 비용에 대해서도 적용됩니다. 도입 당시 180nm 공정을 위한 풀 마스크 세트의 가격은 쉽게 300,000만 달러에 달했고 130nm의 경우 XNUMX만 달러 이상에 달했습니다. 오늘날 그림은 상당히 다릅니다. 글로벌 반도체 협회의 업계 조사에 따르면 지난 180년 동안 60,000nm 마스크 세트 가격은 80,000달러를 넘지 않았으며 130nm 세트의 경우 XNUMX달러 미만인 경우가 많았습니다.

성숙한 프로세스 마스크의 가격이 떨어지기 전에도 ASIC 프로토타입 제작과 심지어 소량 제조에 대한 저렴한 방법 중 하나는 파운드리 TSMC가 선호하는 이름을 사용하는 다중 프로젝트 웨이퍼(MPW) 또는 "셔틀"이었습니다. 이는 대부분의 상용 집적 회로(IC) 크기와 리소그래피 도구가 웨이퍼 표면의 특징을 인쇄하는 데 사용하는 레티클 영역 간의 차이를 활용합니다. 10평방 밀리미터를 측정할 수 있는 레티클에서 600~평방 밀리미터를 차지하는 많은 디자인을 얻을 수 있습니다. 반면에, 귀하가 받을 수 있는 칩의 수는 수십 개로 제한될 수 있지만 잠재적으로 외부 자금 지원이 가능한 지점까지 프로젝트를 진행하기에 충분할 수 있습니다.

마스크 세트는 유일한 초기 엔지니어링 비용과는 거리가 멀습니다. 도구와 IP는 모든 설계에 필수적이며 고급형에서는 쉽게 수백만 달러에 달합니다. 현금이 부족한 설계자를 위한 한 가지 옵션은 Siemens Digital Industries Software 및 IP에서 판매하는 Tanner 제품군과 같은 저렴한 도구에 있습니다. 예를 들어 Arm은 이번 달 초 DesignStart 프로그램을 재조정하여 사전 라이선스 비용 없이 생산 후 로열티만 요구하는 마이크로컨트롤러 중심 코어에 대한 액세스를 제공했습니다.

다른 활동은 Eclipse와 같은 프로젝트를 통해 소프트웨어 개발의 여러 부분에서 발생한 일을 반영합니다. 즉, 오픈 소스 도구를 중심으로 디자인 환경을 구축합니다. 많은 칩 설계 팀은 RTL 검증에 사용되는 테스트 도구를 제어하는 데 선호되는 Python 프로그래밍 언어는 물론 모델링 언어 SystemC를 통해 이미 부분적으로 오픈 소스를 사용하고 있습니다.

오픈소스 이니셔티브

잠재적으로 중요한 이니셔티브는 보다 포괄적인 오픈 소스 설계 도구 세트를 구축하는 것을 목표로 하는 미국 연구 기관 DARPA의 OpenRoad 이니셔티브입니다. 샌디에이고 캘리포니아 대학의 Andrew Kahng 교수이자 이 프로젝트의 수석 연구원은 기계 학습과 그가 "극단적 파티셔닝"이라고 부르는 기술의 조합을 통해 자동으로 다양한 칩 설계를 배치하고 조정할 수 있는 환경을 구상합니다. 독립적으로 최적화된 여러 개의 작은 모듈에 칩을 추가합니다.

검증 엔지니어는 다양한 형태의 오픈 소스를 수용했지만, 테이프아웃이 가까워질수록 도입에 대한 걸림돌은 더 커집니다. 가장 큰 문제는 비공개 계약으로 철저히 보호되고 공유를 금지하는 파운드리에서 제공하는 프로세스 설계 키트(PDK)에 있습니다.

위 및 아래 그림: Antmicro에서 개발한 Caravel 테스트 인프라는 내장된 RISC-V 코어에 의해 관리되는 I/O 및 테스트 포트 링을 제공합니다.

Ansell은 "Efabless는 완전히 재사용 가능한 결과를 공개할 수 없었습니다."라고 말합니다. “나 같은 사람은 게이트에서 무언가가 어떻게 구현되었는지 볼 수 없었습니다. 이 업계에는 공유를 둘러싼 문제적 태도가 있습니다.”

Ansell은 Google이 전반적인 발전을 가속화한다는 기반으로 지식을 공유하는 능력에 관심이 있다고 말합니다. “무어의 법칙으로 인해 계속해서 증가하는 계산 수요를 따라잡기 위해서는 새로운 혁신적인 솔루션이 필요할 것입니다.”라고 그는 덧붙였습니다.

더 넓은 커뮤니티에 실리콘 설계에 대한 액세스를 제공하면 기존 R&D를 통해 실현될 가능성이 적은 새로운 계산 방법을 만들 수 있는 방법을 제공할 수 있습니다. 이를 추진하기 위해 Ansell은 파운드리에게 PDK를 공개하도록 설득하기 시작했습니다. “저는 많은 파운드리들과 이야기를 나눴습니다. 그리고 나는 많은 파운드리들로부터 비웃음을 받았습니다.”

한 파운드리에서는 몇 년 전까지 Cypress Semiconductors가 소유한 미네소타에서 팹을 운영하는 회사인 Skywater라는 아이디어를 생각해 냈습니다. Ansell은 “우리는 오픈 소스 라이센스에 따라 130nm PDK를 출시할 수 있도록 합의할 수 있었습니다.”라고 말했습니다. Github에서 다운로드할 수 있는 PDK는 Apache 2.0 라이센스를 사용하며 “나의 허가나 Skywater의 허가를 구할 필요 없이 모든 사용자가 복제할 수 있습니다. 오픈 소스 PDK는 완전한 오픈 소스 ASIC을 보유할 수 있음을 의미합니다.”

그런 다음 Google과 eFabless는 팹에서 무언가를 되찾기 위해 수만 달러가 없는 사람들에게 ASIC 설계의 가능성을 확장하는 MPW 서비스 구축에 착수했습니다. 무료 칩을 받을 자격을 얻으려면 설계자는 자신의 설계를 오픈 소스로 만들 뿐만 아니라 설계 및 결과 실리콘 작업에 관심이 있는 사용자에게 샘플을 제공할 준비도 해야 합니다. Ansell은 “귀하의 디자인은 GDS에 이르기까지 오픈 소스여야 합니다.”라고 말합니다.

셔틀은 약 XNUMX개의 샘플을 반환할 예정이며, Ansell은 사용자가 요청 시 다른 사용자에게 실리콘을 제공하는 것에 대해 걱정하지 않고 오픈 소스 하드웨어의 공유 가능성을 제공하려고 노력할 수 있을 만큼 충분한 숫자라고 생각합니다. “오픈소스를 사용하면 사람들이 쉽게 협업할 수 있습니다. 이를 통해 사람들은 이전에 너무 위험하다고 생각했던 일을 시도할 수 있습니다. 실패하는 일과 실패로부터 배우는 일이 쉽고 저렴해집니다.”

제약

추가적인 제약은 Antmicro가 개발한 Caravel 테스트 인프라를 사용해야 한다는 요구 사항입니다. 이는 내장된 RISC-V 코어에 의해 관리되는 I/O 링 및 테스트 포트를 제공합니다. Efabless CTO이자 공동 창업자인 Mohammed Kassem은 “처음부터 테스트 칩을 구축하려면 이와 같은 것이 필요합니다.”라고 말합니다. 이 I/O 링 중앙에는 결제 없이 무엇이든 사용할 수 있는 사용자 맞춤형 실리콘을 위한 10제곱밀리미터의 구멍이 있습니다.

면적은 상대적으로 작지만 Ansell은 130nm가 1.5만 개 이상의 게이트를 제공할 수 있으므로 복잡한 디지털 설계를 달성할 수 있다고 말합니다. "사람들은 요즘 저전력 및 아날로그 설계를 목표로 하는 데 주로 사용되기 때문에 구형 노드의 디지털 기능을 크게 과소평가합니다."라고 그는 말합니다.

130nm 공정에 대한 Skywater의 첫 번째 실행 제출은 2020년 XNUMX월에 마감되었으며 두 번째 제출 제출은 XNUMX월 중순에 마감되며 부품은 두 번째 실행에서 XNUMX월 초 프로젝트 소유자에게 전달될 예정입니다. Google은 가까운 시일 내에 셔틀 XNUMX대에 자금을 지원할 예정입니다. Efabless는 또한 완전한 오픈 소스 하드웨어 경로를 사용하고 싶지 않은 설계 팀을 위해 유료 MPW를 제공합니다.

첫 번째 셔틀에는 IBM 및 Quicklogic과 같은 회사의 디자인이 포함되었습니다.

"그러나 가장 흥미로운 점은 디자이너의 60%가 이전에 ASIC을 사용해 본 적이 없다는 것입니다."라고 Ansell은 말합니다. "SkyWater 프로그램의 성공은 개방형 솔루션에 대한 엄청난 수요가 존재하며 이제 다른 주조업체로부터 초기 관심을 받고 있음을 보여줍니다."

고급 노드에 대한 작업으로 인해 설계 비용이 훨씬 더 높아지지만, 결과 칩이 생산에 들어갈 때 잠재적으로 막대한 보상을 받을 수 있지만, 민주화 설계에 대한 후미에서의 작업은 업계의 발전을 추진하는 데 똑같이 중요할 수 있습니다.