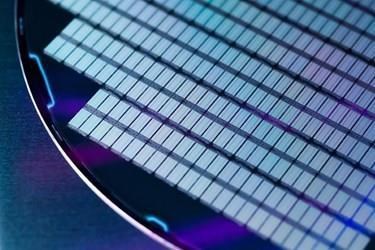

Démocratiser la conception des puces

Alors que le nœud de processus 3 nm approche de la préparation à la production, le coût de développement des puces pour celui-ci a augmenté d'un cran.

Pourtant, il y a une poussée croissante pour démocratiser la conception des puces : la proposer à une communauté plus large d'ingénieurs, à la fois professionnels et amateurs. Cela peut sembler une tâche impossible, mais le mouvement travaille sur des technologies beaucoup plus anciennes car elles deviennent progressivement plus accessibles.

Elle est loin d'être aussi dramatique que la loi de Moore pour les puces à grand volume, mais la courbe d'apprentissage du silicium fonctionne également pour les processus matures, en particulier pour les coûts initiaux tels que la fabrication de masques. Lors de l'introduction, un ensemble complet de masques pour le processus 180 nm pouvait facilement coûter 300,000 130 $ et coûter plus d'un demi-million de dollars pour XNUMX nm. Aujourd'hui, le tableau est tout autre. Le Global Semi-conducteurs L'enquête de l'Association sur l'industrie a révélé au cours des deux dernières années que les prix des ensembles de masques 180 nm n'étaient pas supérieurs à 60,000 80,000 $ et souvent inférieurs à 130 XNUMX $ pour les ensembles XNUMX nm.

Avant même que le prix des masques à processus mature ne baisse, un moyen peu coûteux d'accéder au prototypage ASIC et même à la fabrication à faible volume résidait dans la plaquette multi-projets (MPW) ou « navette », pour utiliser le nom privilégié par la fonderie TSMC. Cela tire parti de la différence entre la taille de la plupart des circuits intégrés (CI) commerciaux et la zone du réticule que l'outil de lithographie utilise pour imprimer des caractéristiques sur la surface de la plaquette. Vous pouvez obtenir de nombreux modèles de 10 à 600 millimètres carrés sur un réticule pouvant mesurer XNUMX millimètres carrés. D'un autre côté, le nombre de puces que vous pouvez choisir de recevoir peut être limité à quelques dizaines, mais potentiellement suffisant pour amener un projet au point où le financement externe est une option.

L'ensemble de masques est loin d'être le seul coût d'ingénierie initial. Les outils et la propriété intellectuelle sont essentiels pour toute conception, qui, dans le haut de gamme, atteint facilement des millions. Une option pour les concepteurs pauvres en argent réside dans des outils moins coûteux, tels que la suite Tanner vendue par Siemens Digital Industries Software et IP. Arm, par exemple, a réorganisé son programme DesignStart plus tôt ce mois-ci, offrant un accès à une sélection de ses cœurs orientés microcontrôleurs sans exiger de frais de licence initiaux, juste des redevances après la production.

D'autres activités reflètent ce qui s'est passé dans de nombreuses parties du développement logiciel avec des projets tels qu'Eclipse : créer un environnement de conception autour d'outils open source. De nombreuses équipes de conception de puces utilisent déjà en partie l'open source, via le langage de modélisation SystemC ainsi que le langage de programmation Python, qui a trouvé la faveur pour contrôler les harnais de test utilisés dans la vérification RTL.

Initiatives open source

Une initiative potentiellement importante est l'initiative OpenRoad de l'agence de recherche américaine DARPA, qui vise à créer un ensemble plus complet d'outils de conception open source. Le professeur Andrew Kahng de l'Université de Californie à San Diego et chercheur principal du projet envisage un environnement qui peut mettre en place et régler automatiquement une gamme de conceptions de puces grâce à une combinaison d'apprentissage automatique et de ce qu'il appelle le « partitionnement extrême », qui divise le puce en de nombreux petits modules optimisés indépendamment.

Bien que les ingénieurs de vérification aient adopté diverses formes d'open source, les obstacles à son adoption deviennent de plus en plus importants à mesure que l'on se rapproche de l'enregistrement. Le plus gros problème réside dans les kits de conception de processus (PDK) fournis par les fonderies qui sont jalousement protégés par des accords de confidentialité et qui interdisent tout partage.

Figures ci-dessus et ci-dessous : L'infrastructure de test Caravel, développée par Antmicro, fournit un anneau d'E/S et de ports de test administrés par un cœur RISC-V intégré

« Efabless n'a pas été en mesure de publier un résultat entièrement réutilisable », note Ansell. « Quelqu'un comme moi ne pouvait pas voir comment quelque chose était mis en œuvre dans les portes. Il y a une attitude problématique dans cette industrie autour du partage.

Ansell dit que Google tient à la capacité de partager des connaissances sur la base qu'elle accélère les progrès en général. « Avec le ralentissement de la loi de Moore, de nouvelles solutions innovantes seront nécessaires pour répondre à la demande toujours croissante de calculs », ajoute-t-il.

Offrir à une communauté plus large un accès à la conception de silicium peut fournir des pistes pour créer de nouvelles méthodes de calcul qui sont moins susceptibles de résulter de la R&D traditionnelle. Pour aider à faire avancer cela, Ansell a commencé à essayer de convaincre les fonderies d'ouvrir leurs PDK. « J'ai parlé à beaucoup de fonderies. Et je me suis moqué de beaucoup de fonderies.

Une fonderie a adhéré à l'idée : Skywater, une entreprise exploitant une usine dans le Minnesota appartenant à Cypress Semiconductors jusqu'à il y a quelques années. « Nous avons pu parvenir à un accord qui nous a permis de publier un PDK 130 nm sous une licence open source », explique Ansell. Téléchargeable depuis Github, le PDK utilise une licence Apache 2.0 et peut être cloné par n'importe quel utilisateur « sans avoir à demander ma permission ou à demander la permission de Skywater. Un PDK open source signifie que nous pouvons avoir des ASIC entièrement open source.

Google et eFabless ont ensuite commencé à créer un service MPW qui étend la possibilité de conception d'ASIC aux personnes sans les dizaines de milliers de dollars pour récupérer quelque chose de la fab. Pour bénéficier des puces gratuites, les concepteurs doivent être prêts non seulement à créer leurs propres conceptions en open source, mais également à fournir des échantillons aux utilisateurs intéressés à travailler avec la conception et le silicium résultant. « Votre conception doit être open source jusqu'au GDS », explique Ansell.

La navette renverra une centaine d'échantillons, ce qu'Ansell considère comme un nombre suffisamment élevé pour que les utilisateurs ne se soucient pas de fournir à d'autres utilisateurs du silicium sur demande et essaient de tirer parti des possibilités de partage du matériel open source. « L'open source permet aux gens de collaborer facilement. Cela permet aux gens d'essayer des choses qu'ils pensaient être trop risquées. Il est facile et peu coûteux d'échouer et d'apprendre de vos échecs.

contraintes

Une autre contrainte est l'obligation d'utiliser l'infrastructure de test Caravel développée par Antmicro. Cela fournit un anneau d'E/S et de ports de test administrés par un cœur RISC-V intégré. « Si vous construisez une puce de test pour commencer, vous avez besoin de quelque chose comme ça », note le CTO et co-fondateur d'Efabless Mohammed Kassem. Au milieu de cet anneau d'E/S se trouve un trou de 10 millimètres carrés pour le silicium personnalisé de l'utilisateur qui peut être utilisé pour n'importe quoi sans paiement.

Bien que la zone soit relativement petite, Ansell affirme que des conceptions numériques complexes sont réalisables car le 130 nm peut fournir plus de 1.5 million de portes. « Les gens sous-estiment largement les capacités numériques des nœuds plus anciens, car ils sont principalement utilisés de nos jours pour cibler les conceptions analogiques et à faible consommation », note-t-il.

Les soumissions pour la première exécution à Skywater sur le processus 130 nm ont été clôturées en novembre 2020 et la seconde se termine pour les soumissions à la mi-juin, les pièces devant être livrées à partir de cette deuxième exécution aux propriétaires de projet début décembre. Google finance six des navettes dans un avenir proche. Efabless propose également MPW payant pour les équipes de conception qui ne souhaitent pas s'engager dans la voie du matériel entièrement open source.

La première navette comprenait des conceptions de sociétés telles qu'IBM et Quicklogic.

"Mais le plus excitant, c'est que 60 % des concepteurs n'ont jamais fait d'ASIC auparavant", déclare Ansell. « Le succès du programme SkyWater montre qu'il existe une énorme demande de solutions ouvertes et nous avons maintenant eu un certain intérêt initial de la part d'autres fonderies. »

Alors que le travail sur des nœuds avancés augmente les coûts de conception, bien qu'avec des récompenses potentiellement énormes lorsque les puces résultantes entrent en production, le travail à la pointe de la démocratisation de la conception peut s'avérer tout aussi important pour faire progresser l'industrie.