Demokratisierung des Chipdesigns

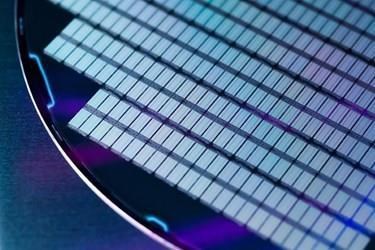

Da sich der 3-nm-Prozessknoten der Produktionsreife nähert, sind die Kosten für die Entwicklung von Chips dafür um eine weitere Stufe gestiegen.

Dennoch gibt es einen wachsenden Druck, das Chipdesign zu demokratisieren: es einer breiteren Gemeinschaft von Ingenieuren zugänglich zu machen, sowohl Profis als auch Amateuren. Dies mag eine unmögliche Aufgabe erscheinen, aber die Bewegung arbeitet an viel älteren Technologien, die allmählich zugänglicher werden.

Es ist bei weitem nicht so dramatisch wie das Mooresche Gesetz für großvolumige Chips, aber die Lernkurve für Silizium funktioniert auch für ausgereifte Prozesse, insbesondere für die Vorlaufkosten wie die Maskenherstellung. Bei der Einführung könnte ein Vollmaskensatz für den 180-nm-Prozess leicht 300,000 US-Dollar kosten und für 130 nm mehr als eine halbe Million US-Dollar betragen. Heute ist das Bild ganz anders. Der Globus Halbleiter Die Branchenumfrage der Association ergab in den letzten zwei Jahren, dass die Preise für 180-nm-Maskensets nicht mehr als 60,000 US-Dollar und oft unter 80,000 US-Dollar für 130-nm-Sets lagen.

Noch bevor ausgereifte Prozessmasken im Preis gefallen sind, war ein kostengünstiger Weg ins ASIC-Prototyping und sogar in die Kleinserienfertigung der Multi-Project-Wafer (MPW) oder „Shuttle“, wie die Foundry TSMC favorisierte. Dies nutzt den Unterschied zwischen der Größe der meisten kommerziellen integrierten Schaltungen (ICs) und der Fläche des Retikels, die das Lithographiewerkzeug verwendet, um Merkmale auf die Oberfläche des Wafers zu drucken. Sie können viele Designs mit einer Größe von 10 bis Quadratmillimetern auf einem Absehen mit einer Größe von 600 Quadratmillimetern erhalten. Auf der anderen Seite kann die Anzahl der Chips, die Sie erhalten können, auf einige Dutzend begrenzt sein, aber möglicherweise ausreichen, um ein Projekt so weit zu bringen, dass eine externe Finanzierung in Frage kommt.

Das Maskenset ist bei weitem nicht der einzige Vorab-Engineering-Kosten. Tools und IP sind für jedes Design von entscheidender Bedeutung, das am oberen Ende leicht in die Millionen geht. Eine Option für zahlungsschwache Designer sind kostengünstigere Tools wie die Tanner-Suite, die von Siemens Digital Industries Software und IP verkauft wird. Arm zum Beispiel hat Anfang dieses Monats sein DesignStart-Programm überarbeitet und bietet Zugang zu einer Auswahl seiner mikrocontrollerorientierten Kerne, ohne eine Vorablizenzgebühr zu verlangen, nur Lizenzgebühren nach der Produktion.

Andere Aktivitäten spiegeln wider, was in vielen Teilen der Softwareentwicklung mit Projekten wie Eclipse passiert ist: Aufbau einer Designumgebung rund um Open-Source-Tools. Viele Chip-Design-Teams verwenden teilweise bereits Open Source, durch die Modellierungssprache SystemC sowie die Programmiersprache Python, die sich für die Steuerung der Test-Harnesses, die bei der RTL-Verifikation verwendet werden, durchgesetzt hat.

Opensource-Initiativen

Eine potenziell wichtige Initiative ist die OpenRoad-Initiative der US-Forschungsagentur DARPA, die darauf abzielt, einen umfassenderen Satz von Open-Source-Designtools zu entwickeln. Professor Andrew Kahng von der University of California in San Diego und leitender Forscher des Projekts sieht eine Umgebung vor, die eine Reihe von Chipdesigns automatisch durch eine Kombination aus maschinellem Lernen und dem, was er "extreme Partitionierung" nennt, auslegen und abstimmen kann, die die Chip in viele kleine, unabhängig optimierte Module.

Obwohl Verifikationsingenieure verschiedene Formen von Open Source angenommen haben, werden die Stolpersteine für die Einführung größer, je näher Sie dem Tape-Out kommen. Das größte Problem sind die von Gießereien bereitgestellten Process Design Kits (PDKs), die streng durch Geheimhaltungsvereinbarungen geschützt sind und jegliche Weitergabe verbieten.

Abbildungen oben und unten: Die von Antmicro entwickelte Caravel-Testinfrastruktur bietet einen Ring von E/A- und Testports, die von einem integrierten RISC-V-Kern verwaltet werden

„Efabless war nicht in der Lage, ein vollständig wiederverwendbares Ergebnis zu veröffentlichen“, bemerkt Ansell. „Jemand wie ich konnte nicht sehen, wie etwas in den Toren umgesetzt wurde. In dieser Branche herrscht eine problematische Einstellung zum Teilen.“

Ansell sagt, dass Google daran interessiert ist, Wissen zu teilen, da es den Fortschritt im Allgemeinen beschleunigt. „Da sich das Mooresche Gesetz verlangsamt, werden neue innovative Lösungen benötigt, um mit der ständig wachsenden Nachfrage nach Berechnungen Schritt zu halten“, fügt er hinzu.

Die Bereitstellung eines Zugangs zum Siliziumdesign für eine breitere Gemeinschaft kann Wege für die Entwicklung neuartiger Berechnungsmethoden eröffnen, die weniger wahrscheinlich durch traditionelle Forschung und Entwicklung entstehen werden. Um dies voranzutreiben, versuchte Ansell, Gießereien davon zu überzeugen, ihre PDKs zu öffnen. „Ich habe mit vielen Gießereien gesprochen. Und ich wurde von vielen Gießereien ausgelacht.“

Eine Gießerei kam auf die Idee: Skywater, ein Unternehmen, das bis vor einigen Jahren eine Fabrik in Minnesota im Besitz von Cypress Semiconductors betreibt. „Wir konnten eine Vereinbarung treffen, die es uns ermöglichte, ein 130-nm-PDK unter einer Open-Source-Lizenz zu veröffentlichen“, sagt Ansell. Das von Github herunterladbare PDK verwendet eine Apache 2.0-Lizenz und kann von jedem Benutzer geklont werden, „ohne meine Erlaubnis oder die Erlaubnis von Skywater einholen zu müssen. Ein Open-Source-PDK bedeutet, dass wir vollständig Open-Source-ASICs haben können.“

Google und eFabless machten sich dann daran, einen MPW-Dienst aufzubauen, der die Möglichkeit des ASIC-Designs auf Menschen ausdehnt, die nicht die Zehntausende von Dollar haben, um etwas von der Fab zurückzubekommen. Um sich für die kostenlosen Chips zu qualifizieren, müssen Designer nicht nur darauf vorbereitet sein, ihre eigenen Designs Open Source zu erstellen, sondern auch darauf vorbereitet sein, Muster an Benutzer zu liefern, die daran interessiert sind, mit dem Design und dem resultierenden Silizium zu arbeiten. „Ihr Design muss bis hin zum GDS Open Source sein“, sagt Ansell.

Das Shuttle wird rund hundert Samples zurücksenden, was Ansell als hoch genug ansieht, damit sich die Nutzer keine Sorgen machen müssen, anderen Nutzern auf Anfrage Silizium zur Verfügung zu stellen und versuchen, die Sharing-Möglichkeiten von Open-Source-Hardware zu liefern. „Open Source macht es den Menschen leicht, zusammenzuarbeiten. Dies ermöglicht es den Menschen, Dinge zu versuchen, die sie früher für zu riskant hielten. Es macht es einfach und billig, zu scheitern und aus seinen Fehlern zu lernen.“

Einschränkungen

Eine weitere Einschränkung ist die Anforderung, die von Antmicro entwickelte Caravel-Testinfrastruktur zu nutzen. Dadurch wird ein Ring von E/A- und Testports bereitgestellt, die von einem integrierten RISC-V-Kern verwaltet werden. „Wenn Sie zu Beginn einen Testchip bauen, brauchen Sie so etwas“, bemerkt Efabless CTO und Mitbegründer Mohammed Kassem. In der Mitte dieses I/O-Rings befindet sich ein 10 Quadratmillimeter großes Loch für das benutzerdefinierte Silizium des Benutzers, das ohne Bezahlung für alles verwendet werden kann.

Obwohl das Gebiet relativ klein ist, sagt Ansell, dass komplexe digitale Designs erreichbar sind, da 130 nm mehr als 1.5 Millionen Gates liefern können. „Die Leute unterschätzen die digitalen Fähigkeiten älterer Knoten bei weitem, da sie heutzutage hauptsächlich für stromsparende und analoge Designs verwendet werden“, bemerkt er.

Die Einreichungen für den ersten Lauf bei Skywater im 130-nm-Prozess endeten im November 2020 und der zweite endete für die Einreichungen Mitte Juni, wobei die Teile aus diesem zweiten Lauf Anfang Dezember an die Projektbesitzer geliefert werden sollen. Google finanziert in naher Zukunft sechs der Shuttles. Efabless bietet auch kostenpflichtige MPW für Designteams an, die sich nicht auf den vollständig Open-Source-Hardwareweg festlegen möchten.

Der erste Shuttle umfasste Designs von Unternehmen wie IBM und Quicklogic.

„Aber das Spannendste war, dass 60 Prozent der Designer noch nie zuvor einen ASIC erstellt haben“, sagt Ansell. „Der Erfolg des SkyWater-Programms zeigt, dass eine große Nachfrage nach offenen Lösungen besteht und wir nun auch von anderen Gießereien erste Interesse geweckt haben.“

Während die Arbeit an fortschrittlichen Nodes die Designkosten immer weiter in die Höhe treibt, wenn auch mit potenziell enormen Belohnungen, wenn die resultierenden Chips in Produktion gehen, kann sich die Arbeit an der Hinterkante zur Demokratisierung des Designs als ebenso wichtig erweisen, um den Fortschritt in der Branche voranzutreiben.