Dân chủ hóa thiết kế chip

Khi nút quy trình 3nm gần sẵn sàng sản xuất, chi phí phát triển chip cho nó đã tăng lên một bậc khác.

Tuy nhiên, ngày càng có nhiều nỗ lực để dân chủ hóa thiết kế chip: đưa nó đến với một cộng đồng kỹ sư rộng lớn hơn, cả chuyên nghiệp và nghiệp dư. Đây có vẻ là một nhiệm vụ bất khả thi nhưng phong trào đang hoạt động trên các công nghệ cũ hơn nhiều khi chúng dần trở nên dễ tiếp cận hơn.

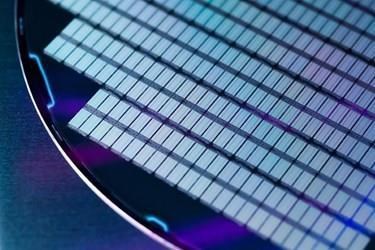

Nó không ấn tượng bằng Định luật Moore đối với chip khối lượng lớn nhưng đường cong học tập silicon cũng hoạt động cho các quy trình trưởng thành, đặc biệt là đối với các chi phí trả trước như chế tạo mặt nạ. Khi được giới thiệu, một bộ mặt nạ đầy đủ cho quy trình 180nm có thể dễ dàng có giá 300,000 đô la và lên tới hơn nửa triệu đô la cho quy trình 130nm. Hôm nay bức tranh đã khác khá nhiều. Toàn cầu Semiconductor Khảo sát ngành của Hiệp hội cho thấy trong hai năm qua, giá bộ mặt nạ 180nm không quá 60,000 USD và thường dưới 80,000 USD cho bộ 130nm.

Ngay cả trước khi mặt nạ quy trình trưởng thành giảm giá, một cách chi phí thấp để tạo mẫu ASIC và thậm chí sản xuất khối lượng thấp nằm trong tấm wafer đa dự án (MPW) hoặc "con thoi", sử dụng cái tên được ưa chuộng bởi xưởng đúc TSMC. Điều này tận dụng sự khác biệt giữa kích thước của hầu hết các mạch tích hợp thương mại (IC) và diện tích của kẻ ô mà công cụ in thạch bản sử dụng để in các tính năng trên bề mặt của tấm wafer. Bạn có thể nhận được rất nhiều thiết kế có kích thước lên đến 10 đến milimét vuông trên một ô có thể có kích thước 600 milimét vuông. Mặt khác, số lượng chip mà bạn có thể chọn nhận có thể bị giới hạn ở chỉ vài chục nhưng đủ tiềm năng để thực hiện một dự án đến mức tài trợ bên ngoài là một lựa chọn.

Bộ mặt nạ không phải là chi phí kỹ thuật trả trước duy nhất. Công cụ và IP là yếu tố quan trọng đối với bất kỳ thiết kế nào, mà ở cấp cao hơn dễ dàng có hàng triệu. Một lựa chọn cho các nhà thiết kế không có nhiều tiền nằm trong các công cụ chi phí thấp hơn, chẳng hạn như bộ Tanner do Siemens Digital Industries Software và IP bán. Ví dụ, Arm đã khởi động lại chương trình DesignStart vào đầu tháng này, cung cấp quyền truy cập vào lựa chọn các lõi hướng vi điều khiển mà không yêu cầu phí cấp phép trả trước, chỉ cần tiền bản quyền sau khi sản xuất.

Các hoạt động khác phản ánh những gì đã xảy ra trong nhiều phần phát triển phần mềm với các dự án như Eclipse: xây dựng môi trường thiết kế xung quanh các công cụ mã nguồn mở. Nhiều nhóm thiết kế chip đang sử dụng một phần mã nguồn mở, thông qua ngôn ngữ mô hình hóa SystemC cũng như ngôn ngữ lập trình Python, đã tìm thấy lợi ích cho việc kiểm soát các khai thác thử nghiệm được sử dụng trong xác minh RTL.

Các sáng kiến nguồn mở

Một sáng kiến có khả năng quan trọng là sáng kiến OpenRoad của cơ quan nghiên cứu Hoa Kỳ DARPA, nhằm mục đích xây dựng một bộ công cụ thiết kế mã nguồn mở toàn diện hơn. Giáo sư Andrew Kahng của Đại học California tại San Diego và điều tra viên chính của dự án dự kiến một môi trường có thể bố trí và điều chỉnh một loạt các thiết kế chip tự động thông qua sự kết hợp của máy học và cái mà ông gọi là "phân vùng cực đoan", phân chia chip thành nhiều mô-đun nhỏ được tối ưu hóa độc lập.

Mặc dù các kỹ sư xác minh đã chấp nhận nhiều dạng mã nguồn mở khác nhau, nhưng những trở ngại cho việc áp dụng nó càng lớn khi bạn càng tiến gần đến việc loại bỏ. Vấn đề lớn nhất nằm ở bộ dụng cụ thiết kế quy trình (PDK) được cung cấp bởi các xưởng đúc được bảo vệ một cách ghen tị bởi các thỏa thuận không tiết lộ và cấm mọi chia sẻ.

Hình bên trên và bên dưới: Cơ sở hạ tầng thử nghiệm Caravel, do Antmicro phát triển, cung cấp một vòng I / O và các cổng thử nghiệm được quản lý bởi lõi RISC-V tích hợp

“Efabless không thể phát hành một kết quả hoàn toàn có thể tái sử dụng,” Ansell lưu ý. “Một người như tôi không thể nhìn vào cách một cái gì đó được thực hiện trong các cánh cổng. Có một thái độ có vấn đề trong ngành công nghiệp này xung quanh việc chia sẻ. ”

Ansell cho biết Google rất quan tâm đến khả năng chia sẻ kiến thức trên cơ sở thúc đẩy sự tiến bộ nói chung. Ông cho biết thêm: “Với định luật Moore, các giải pháp sáng tạo mới sẽ cần thiết để theo kịp với nhu cầu tính toán ngày càng tăng.

Cung cấp cho một cộng đồng rộng lớn hơn quyền truy cập vào thiết kế silicon có thể cung cấp các con đường để tạo ra các phương pháp tính toán mới mà ít có khả năng xảy ra thông qua R&D truyền thống. Để giúp thúc đẩy điều đó, Ansell bắt đầu cố gắng thuyết phục các xưởng đúc mở PDK của họ. “Tôi đã nói chuyện với rất nhiều xưởng đúc. Và tôi đã bị rất nhiều xưởng đúc cười nhạo. "

Một xưởng đúc đã nảy ra ý tưởng: Skywater, một công ty điều hành xưởng sản xuất ở Minnesota thuộc sở hữu của Cypress Semiconductors cách đây vài năm. “Chúng tôi đã có thể đi đến một thỏa thuận cho phép chúng tôi phát hành PDK 130nm theo giấy phép nguồn mở,” Ansell nói. Có thể tải xuống từ Github, PDK sử dụng giấy phép Apache 2.0 và có thể được sao chép bởi bất kỳ người dùng nào “mà không cần phải xin phép tôi hoặc phải xin phép Skywater. Một PDK mã nguồn mở có nghĩa là chúng ta có thể có các ASIC hoàn toàn mã nguồn mở. ”

Google và eFabless sau đó bắt đầu xây dựng một dịch vụ MPW mở rộng khả năng thiết kế ASIC cho những người không có hàng chục nghìn đô la để lấy lại thứ gì đó từ người dùng. Để đủ điều kiện nhận chip miễn phí, các nhà thiết kế cần phải chuẩn bị để không chỉ tạo ra các thiết kế của riêng họ ở mã nguồn mở mà họ còn cần chuẩn bị để cung cấp các mẫu cho những người dùng quan tâm đến thiết kế và kết quả là silicon. Ansell nói: “Thiết kế của bạn phải là mã nguồn mở từ đầu đến cuối GDS.

Tàu con thoi sẽ trả về khoảng một trăm mẫu, mà Ansell coi là con số đủ cao để người dùng không phải lo lắng về việc cung cấp silicon cho người dùng khác theo yêu cầu và cố gắng cung cấp khả năng chia sẻ của phần cứng nguồn mở. “Mã nguồn mở giúp mọi người dễ dàng cộng tác. Điều này cho phép mọi người thử những thứ mà họ từng nghĩ là quá rủi ro. Nó giúp bạn thất bại dễ dàng và rẻ tiền, và học hỏi từ những thất bại của bạn ”.

Những ràng buộc

Một hạn chế nữa là yêu cầu sử dụng cơ sở hạ tầng thử nghiệm Caravel do Antmicro phát triển. Điều này cung cấp một vòng I / O và các cổng kiểm tra được quản lý bởi một lõi RISC-V tích hợp sẵn. “Nếu bạn đang xây dựng một con chip thử nghiệm để bắt đầu, bạn cần một cái gì đó như thế này,” CTO Efabless và đồng sáng lập Mohammed Kassem lưu ý. Ở giữa vòng I / O này là một lỗ 10 mm vuông cho silicon tùy chỉnh của người dùng có thể được sử dụng cho bất kỳ thứ gì mà không cần thanh toán.

Mặc dù diện tích tương đối nhỏ, Ansell cho biết có thể đạt được các thiết kế kỹ thuật số phức tạp vì 130nm có thể cung cấp hơn 1.5 triệu cổng. "Mọi người đánh giá thấp khả năng kỹ thuật số của các nút cũ hơn bởi vì chúng hầu như được sử dụng ngày nay để nhắm mục tiêu công suất thấp và thiết kế tương tự," ông lưu ý.

Các bản đệ trình cho lần chạy đầu tiên tại Skywater trên quy trình 130nm kết thúc vào tháng 2020 năm XNUMX và lần thứ hai kết thúc để đệ trình vào giữa tháng XNUMX, với các bộ phận sẽ được chuyển từ lần chạy thứ hai đó cho các chủ dự án vào đầu tháng XNUMX. Google sẽ tài trợ cho sáu trong số các tàu con thoi trong tương lai gần. Efabless cũng cung cấp MPW trả phí cho các nhóm thiết kế không muốn cam kết với lộ trình phần cứng hoàn toàn mã nguồn mở.

Tàu con thoi đầu tiên bao gồm các thiết kế của các công ty như IBM và Quicklogic.

“Nhưng điều thú vị nhất là 60% các nhà thiết kế chưa từng làm ASIC trước đây,” Ansell nói. “Sự thành công của chương trình SkyWater cho thấy nhu cầu rất lớn về các giải pháp mở và chúng tôi hiện đã có một số quan tâm ban đầu từ các xưởng đúc khác.”

Trong khi công việc trên các nút nâng cao đẩy chi phí thiết kế lên cao hơn bao giờ hết, mặc dù có khả năng phần thưởng khổng lồ khi các chip kết quả đi vào sản xuất, công việc ở điểm cuối về thiết kế dân chủ hóa có thể chứng tỏ tầm quan trọng không kém trong việc thúc đẩy tiến bộ trong ngành.